# Strong Logic for Weak Memory: Reasoning About Release-Acquire Consistency in Iris<sup>\*†</sup>

Jan-Oliver Kaiser<sup>1</sup>, Hoang-Hai Dang<sup>2</sup>, Derek Dreyer<sup>3</sup>, Ori Lahav<sup>4</sup>, and Viktor Vafeiadis<sup>5</sup>

- 1 MPI-SWS, Saarbrücken and Kaiserslautern, Germany<sup>‡</sup> janno@mpi-sws.org

- 2 MPI-SWS, Saarbrücken and Kaiserslautern, Germany<sup>†</sup> haidang@mpi-sws.org

- 3 MPI-SWS, Saarbrücken and Kaiserslautern, Germany<sup>†</sup> dreyer@mpi-sws.org

- 4 MPI-SWS, Saarbrücken and Kaiserslautern, Germany<sup>†</sup> orilahav@mpi-sws.org

- 5 MPI-SWS, Saarbrücken and Kaiserslautern, Germany<sup>†</sup> viktor@mpi-sws.org

## — Abstract

The field of *concurrent separation logics* (CSLs) has recently undergone two exciting developments: (1) the *Iris framework* for encoding and unifying advanced higher-order CSLs and formalizing them in Coq, and (2) the adaptation of CSLs to account for *weak memory models*, notably C11's release-acquire (RA) consistency. Unfortunately, these developments are seemingly incompatible, since Iris only applies to languages with an operational interleaving semantics, while C11 is defined by a declarative (axiomatic) semantics. In this paper, we show that, on the contrary, it is not only feasible but useful to marry these developments together. Our first step is to provide a novel operational characterization of RA+NA, the fragment of C11 containing RA accesses and "non-atomic" (normal data) accesses. Instantiating Iris with this semantics, we then derive higher-order variants of two prominent RA+NA logics, GPS and RSL. Finally, we deploy these derived logics in order to perform the first mechanical verifications (in Coq) of several interesting case studies of RA+NA programming. In a nutshell, we provide the first foundationally verified framework for proving programs correct under C11's weak-memory semantics.

**1998 ACM Subject Classification** F.3.1 Specifying and Verifying and Reasoning about Programs; F.3.2 Semantics of Programming Languages

Keywords and phrases Weak memory models, release-acquire, concurrency, separation logic

Digital Object Identifier 10.4230/LIPIcs.ECOOP.2017.17

**Supplementary Material** ECOOP Artifact Evaluation approved artifact available at http://dx.doi.org/10.4230/DARTS.3.2.15

<sup>&</sup>lt;sup>‡</sup> Saarland Informatics Campus.

LIPICS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

<sup>\*</sup> An extended version of this paper with a technical appendix can be found at [1].

<sup>&</sup>lt;sup>†</sup> This research was supported in part by a European Research Council (ERC) Consolidator Grant for the project "RustBelt", funded under the European Union's Horizon 2020 Framework Programme (grant agreement no. 683289).

Leibniz International Proceedings in Informatics

## 17:2 Strong Logic for Weak Memory

## 1 Introduction

Separation logic [25] is a refinement of Hoare logic with an intrinsic notion of ownership: whereas an assertion in Hoare logic denotes a fact about the global machine state, an assertion in separation logic denotes ownership of (and knowledge about) a piece of that state, and the separating conjunction P \* Q denotes that the assertions P and Q own disjoint pieces of state. This ownership reading of assertions is useful for giving "local" (or "smallfootprint") specifications for primitive commands, which are much easier to compose soundly into specifications for larger programs. Moreover, as O'Hearn was the first to observe [24], separation logic is also eminently suitable for concurrent programs. In particular, ownership provides a direct and convenient way of explaining how synchronization mechanisms serve to transfer control of shared state between threads. Although O'Hearn's original concurrent version of separation logic was geared toward reasoning about coarse-grained synchronization via semaphores, the subsequent decade of research into concurrent separation logics (CSLs) has shown that ownership and separation are just as useful for reasoning about more fine-grained and low-level synchronization mechanisms, such as those employed in the implementations of non-blocking data structures [35, 11, 7, 32, 30, 23, 6].

In this paper, we consider two of the most recent, boundary-pushing developments in concurrent separation logics: (1) the *Iris framework* for encoding and unifying advanced higher-order CSLs and formalizing them in Coq [14, 13, 16, 17], and (2) the adaptation of CSLs to account for *weak memory models*, notably C11's *release-acquire* (RA) consistency [34, 33, 8, 20]. Although these developments have thus far (for reasons explained below) appeared to be incompatible, we show that in fact they are not! Quite the contrary: we demonstrate that it is not only feasible but useful to marry them together, and in so doing, provide the first foundationally verified framework for proving programs correct under C11's weak memory semantics.

## 1.1 Iris: A Unifying Framework for Concurrent Separation Logics

After O'Hearn's original CSL, there came a steady stream of "new and improved" CSLs appearing on at least a yearly basis. Unfortunately, as these new CSLs grew ever more expressive, they also grew increasingly complex, baking in increasingly sophisticated proof rules as primitive, with the relationships and compatibility between different proof rules (*e.g.*, whether they could be soundly combined in one logic) remaining unclear.

The central source of complexity in most existing CSLs lies in their mechanisms for controlling *interference* between threads accessing shared state, which have evolved from Jones's *rely-guarantee* [12] to the much more sophisticated and elaborate *protocol* mechanisms appearing in logics like CaReSL [32], iCAP [30], and TaDA [6]. In an attempt to consolidate the field, Jung *et al.* developed **Iris** [14, 13, 16], a logic with the express goal of showing that even the fanciest of these interference-control mechanisms could be encoded via a combination of two orthogonal "off-the-shelf" ingredients: (1) *partial commutative monoids* (PCMs) for formalizing protocols on shared state, and (2) *invariants* for enforcing them. Invariants are an old and ubiquitous concept in program verification, and PCMs have been used in a number of prior logics to represent different kinds of *ghost* (or *auxiliary*) state *i.e.*, logical state that is manipulated as part of the proof of a program but is not manipulated directly by the program itself. Jung *et al.*'s observation was that in fact these two simple mechanisms are all you need: using just PCMs and invariants, one can *derive* a variety of powerful forms of protocol-based reasoning from prior CSLs *within* Iris, and by virtue of working in a unified framework, these derived mechanisms are automatically compatible (different mechanisms can be used

soundly to verify different modules in a program). It is also goes beyond most prior CSLs by supporting higher-order quantification and *impredicative invariants*—invariants that can talk recursively about the existence of (other) invariants—which are crucial for reasoning about languages with higher-order state (*e.g.*, Rust).

In the past, the complexity of CSLs was further exacerbated by the fact that (until very recently [27]) they only supported manual and error-prone "pencil-and-paper" proofs. The initial version of Iris [14] was no exception: the *soundness* of the core logic was verified in Coq, but the Coq development provided no support for *using* the logic (either to encode other logics or to verify programs interactively). However, in the past year, Krebbers *et al.* [17] have developed IPM, an interactive proof mode geared toward using Iris as a proof development environment for verifying concurrent programs within Coq. With IPM, Iris has begun the transition to a more practically useful proof tool, and is already being deployed effectively for larger verification efforts, *e.g.*, in the RustBelt project [10].

## 1.2 Separation Logics for Release-Acquire Consistency

Iris is a "generic" logical framework in that it is parameterized over the programming language in question—it merely requires, like the vast majority of prior work on concurrent program verification, that the language have an *operational, interleaving semantics*, typically known as a *sequentially consistent* (SC) semantics [21]. Under SC, threads take turns accessing the shared memory, and updates to memory are immediately visible to all other threads.

SC semantics has the benefit that it is easy to define and manipulate formally, but it is also woefully unrealistic: no serious language guarantees a fully SC semantics, because of the significant performance costs associated with maintaining the fiction of a single, globally consistent view of memory on modern multi-core architectures. One of the reasons for this discrepancy between the theory and the reality of concurrent programming is that, until relatively recently, formal accounts of more realistic—so-called *weak* (or *relaxed*)—memory models for concurrent programming languages were not available. However, in the past decade, great progress has been made on formalizing weak memory models, with a notable high point being the formalization of the C/C++11 memory model (hereafter, C11) [4].

In response to this development, a number of verification researchers have followed suit by building new verification tools—program logics, model checkers, testing frameworks, etc.—that account for these more realistic memory models. In particular, Vafeiadis and collaborators have thus far developed several different separation logics for C11, including RSL [34] and GPS [33]. The main focus of these logics is on RA+NA, an important fragment of C11 consisting of *release-acquire* (RA) accesses and *non-atomic* (NA) accesses. RA accesses are useful because they support a common idiom of message-passing synchronization at low cost compared to SC. NA accesses are intended for "normal" data accesses and are even more efficiently implementable than RA accesses, with the proviso that they are not permitted to race (*i.e.*, races on non-atomics cause the entire program to have undefined behavior).

A major challenge that Vafeiadis *et al.* had to overcome was the fact that C11 is defined using a radically different semantics than SC. Specifically, it is defined by a *declarative* (or *axiomatic*) semantics, in which the allowed behaviors of a program are defined by enumerating candidate executions (represented as "event graphs") and then restricting attention to the executions that obey various coherence axioms. In building separation logics for C11, Vafeiadis *et al.* were thus not able to use the standard model of Hoare-style program specifications from prior separation logics because notions like "the machine states before and after executing a command C" do not have a clear meaning in C11's declarative semantics.

To account for this radically different type of semantics, they were instead forced to essentially throw away the "separation-logic textbook" and come up with an entirely new,

## 17:4 Strong Logic for Weak Memory

non-standard model of separation logic in terms of predicates on event graphs. While groundbreaking, this approach has had several downsides. Firstly, certain essential mechanisms of SC-based separation logic (such as ghost state), which are easy to justify in standard models, became very difficult to justify in the new event-graph-based models of RA+NA logics. Secondly, the complexity of these new models has made them challenging to adapt and extend, and their non-standard nature has posed a major accessibility hurdle for researchers accustomed to traditional models of separation logic. Last but not least, although the soundness of these logics has been verified formally in Coq, there has thus far been no tool support for using the logics to prove programs correct under RA+NA semantics.

## 1.3 Our Contributions

Given our above description, it may seem that the Iris framework's reliance on interleaving semantics renders it fundamentally inapplicable to reasoning about C11's weak-memory semantics. In this paper, we show that this is not the case at all—not only is it possible to derive RA+NA logics like GPS and RSL within Iris, but there are several tangible benefits to doing so. Deriving such logics within Iris:

- Lets us take advantage of the rich features of the Iris host logic (*e.g.*, separation, invariants) when proving soundness of the derived logics, thereby significantly lifting the abstraction level at which those soundness proofs are carried out (compared to prior work).

- Allows us to support some very useful features in our derived logics by directly importing them from Iris. Such features include PCM-based ghost state, higher-order impredicative quantification, and Iris's interactive proof mode in Coq. By virtue of being encoded in Iris, our derived logics inherit these features for free.

- Makes it easy to experiment with the derived logics and quickly develop new and useful extensions (e.g., single-writer protocols, see below).

- Makes it possible to soundly compose proofs from different derived logics, since they are all carried out in the uniform framework of Iris.

Our first step (Section 2) is to avoid the essential complicating factor—C11's declarative account of RA+NA—and instead work with an operational account. Building closely on Lahav *et al.*'s recently proposed "strong release-acquire" (SRA) semantics [19], we define a novel, operational, interleaving semantics for RA+NA. Our operational account of the RA fragment of the language is very similar to Lahav *et al.*'s operational account of SRA in that it models writing and reading of memory via the sending and receiving of timestamped messages; the main difference is that the RA rule for assigning timestamps is slightly more liberal. Our account of NA is new, though; it uses timestamps to model races on non-atomics as stuck (unsafe) machine states. We have proven that, under the reasonable restriction that programs do not mix RMWs (atomic updates) and non-atomic reads at the same location, our semantics is equivalent to the standard declarative semantics of the RA+NA fragment of C11.

Next, since our new semantics for RA+NA is an interleaving semantics, we can instantiate Iris with it. In Section 3, we review the basic reasoning mechanisms of Iris, and show how to use them to derive small-footprint proof rules for reasoning about RA+NA programs. We apply these rules to verify a simple message-passing example of RA+NA programming in Iris. However, as will become clear, reasoning directly with the Iris primitive mechanisms is rather too low-level and a more abstract logic is needed.

In Section 4, we present iGPS, a higher-order variant of Turon *et al.*'s GPS logic [33], which supports much higher-level reasoning about RA+NA programs. Unlike the original

GPS, iGPS is derived within Iris on top of the small-footprint proof rules from Section 3. It also extends GPS with *single-writer protocols*, an extremely useful feature that simplifies proofs of RA+NA programs in the common case where there are no write-write races on atomic accesses.

In Section 5, we briefly describe some other contributions, including iRSL, a higher-order variant of RSL [34] derived within Iris, and several case studies that we have verified using iGPS and iRSL in Coq. These examples showcase one of the major advantages of working in the Iris framework: our ability to verify weak-memory programs, foundationally and mechanically, with the same degree of ease that was previously only possible for SC programs.

Finally, in Section 6, we conclude with related work.

## 2 Release-Acquire and Non-Atomics

In this section, we introduce our operational semantics for RA+NA, which we then use as the machine for our working language  $\lambda_{\rm RN}$ . Subsequent sections will show how to build a logic for  $\lambda_{\rm RN}$  using Iris.

C11 provides several memory access modes, each ensuring a different degree of consistency. In this paper we focus on RA+NA, the fragment of C11 consisting only of release-acquire (RA) and non-atomic (NA) accesses. Non-atomic accesses (which we denote with "[na]") are the default type of memory accesses, intended to be used for normal data rather than for synchronization. Thus, C11 forbids any data races on non-atomic accesses, and programs that may have such races are considered buggy (they have undefined semantics). In contrast, RA accesses (which we denote with "[at]" for *atomic*) are permitted to race, but provide just enough consistency guarantees to enable the well-known *message passing* (MP) idiom:

Initially, both variables x and y are set to 0. The first thread will initialize x to 37 (nonatomically) and then set the variable y to 1 (via a release write) as a way of sending a message to the second thread that x has been properly initialized and is ready for consumption. The second thread will repeatedly read y (via an acquire read) until it observes  $y \neq 0$ , at which point—thanks to release-acquire semantics—it will know that it can safely access x. Summing up, the use of RA here ensures that the non-atomic write to x in the first thread "happens before" the non-atomic read of x in the second thread—*i.e.*, that they do not race—and furthermore that the read of x will return 37.

The formal semantics of RA+NA is "declarative", formulated as a set of constraints on execution graphs. We will instead now present an alternative *operational* semantics of RA+NA. Our operational semantics is not completely coherent with C11's for programs that mix atomic and non-atomic accesses to the same location (although the semantics of such programs is already known to be problematic [3]—see Section 6 for further discussion of this point). However, for the large class of programs that do not mix atomic updates (like CAS) and non-atomic reads at the same location, our semantics is provably equivalent to C11's declarative semantics. This class of programs includes all C11 programs considered (and verified) in this paper. (For formal details of the correspondence between our semantics and C11's, see our technical appendix [1].) We will first start with the pure RA fragment, and then add a "race detector" for non-atomic accesses.

#### 17:6 Strong Logic for Weak Memory

## 2.1 Release-Acquire

Our operational semantics for RA starts from the observation that in RA—in contrast to a standard heap language—different threads have a different view of what the state is. Accordingly, we need to keep track of past write events as they might still be relevant for some subset of threads. Moreover, we need to keep writes to the same location in a total order enforced in C11 under the name *modification order* (*mo* for short). Finally, we also need to keep track of each thread's "progress" in terms of which writes are visible to it, as this determines what a thread may read and where its writes may end up.

For the *mo* order, the RA machine manages for each location a totally ordered set of timestamps  $t \in \text{Time} \triangleq \mathbb{N}$ . Each write of some value v to a location  $\ell$  gets assigned a timestamp (that is unique for  $\ell$ ), resulting in a write event  $\omega \in \text{Event} \triangleq \text{Loc} \times \text{Val} \times \text{Time}$ , where  $v \in \text{Val} \triangleq \mathbb{Z}$ .<sup>1</sup> Using timestamps, the thread's "progress" is represented by a *view*,  $V \in \text{View} \triangleq \text{Loc} \stackrel{\text{fin}}{\rightharpoonup} \text{Time}$ , which records the timestamp of the most recent write event observed by the thread for every location. To enable communication between threads, every write event is augmented with the writing thread's view, yielding a message  $m \in \text{Msg} \triangleq \text{Event} \times \text{View}$ . The machine state  $\sigma$  comprises a message pool (called *memory*) and a view for every thread.

▶ Definition 1 (Simplified Physical State). Let  $\sigma \in \Sigma \triangleq \left(\mathcal{P}(Msg) \times (ThreadId \stackrel{\text{fin}}{\longrightarrow} View)\right) \uplus \{\perp_{uninit}\}$  represent physical machine states, where  $\perp_{uninit}$  represents an error state. We write M and T to denote the two components of a non-error state.

The  $\lambda_{\rm RN}$  language's reductions are factored into *expression reductions*, concerned with the evaluation of the language's expressions, and *machine reductions*, concerned with how the execution of an expression affects the machine state. We will define the expression reductions later when we formally define  $\lambda_{\rm RN}$ . Here we focus on the machine reductions.

We define event labels  $\varepsilon \in \mathcal{E} \triangleq \{ \langle \text{Read}, \ell, v \rangle, \langle \text{Write}, \ell, v \rangle, \langle \text{Update}, \ell, v_o, v_n \rangle, \langle \text{Fork}, \rho \rangle \}$ , representing reads, writes, atomic updates (RMW's), and forks (with  $\rho$  being the newly created thread id), respectively. The reductions are defined by a set of local, per-thread reductions  $\xrightarrow{\varepsilon} \pi \subseteq \Sigma \times \Sigma$  given in Figure 1, where  $\pi$  represents the current thread's id.

A write (THREAD-WRITE) picks an *unused* timestamp t for location  $\ell$  that is greater than the thread's view of  $\ell$ , updates the thread's view to the new view V' that includes t, and adds a corresponding message to the memory. A read (THREAD-READ) incorporates the view V of the message that it reads into the thread's own view.<sup>2</sup> Note that the message being read is required to have a timestamp that is not smaller than the thread's view of the relevant location. Updates (THREAD-UPDATE) combine reading and writing in one step. In addition, updates must "pick" t + 1 as a timestamp for the new message, where t is the timestamp of the read message. This implies, in particular, that two different updates cannot read the same message, and corresponds to C11's atomicity condition, which requires every update to read from its *mo*-immediate predecessor. THREAD-FORK adds a new thread whose view is copied from its parent. Finally, THREAD-UNINITIALIZED detects reads from uninitialized locations, and moves to the error state  $\perp_{uninit}$ .

<sup>&</sup>lt;sup>1</sup> The full semantics also supports allocation, which induces an allocation value A. We do not mention it here for the sake of simplicity.

<sup>&</sup>lt;sup>2</sup> Here, we use the join operator  $\sqcup$  on views:  $(V_1 \sqcup V_2)(\ell) = \max\{V_1(\ell), V_2(\ell)\}$  if  $\ell \in \operatorname{dom}(V_1) \cap \operatorname{dom}(V_2)$ ;  $(V_1 \sqcup V_2)(\ell) = V_i(\ell)$  if  $\ell \in \operatorname{dom}(V_i) \setminus \operatorname{dom}(V_j)$ ; and  $(V_1 \sqcup V_2)(\ell)$  is undefined if  $\ell \notin \operatorname{dom}(V_1) \cup \operatorname{dom}(V_2)$ .

| $\frac{\overset{\text{Thread-Read}}{(\ell, v, t, V) \in M}}{(M, T) \xrightarrow{(\text{Read}, \ell, v)}{\pi}} (M, T)$                                                   |                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\frac{\overset{\text{Thread-WRITE}}{\neg \exists v', V. \ (\ell, v', t, V) \in M} T(\tau)}{(M, T) \xrightarrow{\langle \text{Write}, \ell, v \rangle} \pi} (M \cup \{$ | $T(\ell) < t$ $V' = T(\pi)[\ell \mapsto t]$                                                                                                                                                                                                        |

| Thread-Update<br>$(\ell, v_o, t, V) \in M$<br>$\neg \exists v, V. \ (\ell, v, t+1, V) \in M$                                                                            | $T(\pi)(\ell) \le t$ $V' = T(\pi)[\ell \mapsto t+1] \sqcup V$                                                                                                                                                                                      |

| $(M, T) \xrightarrow{(\text{Update}, \ell, v_o, v_n)} \pi (M \cup \{T_{\text{HREAD-FORK}} \rho \notin \text{dom}(T)$                                                    | $ \begin{array}{l} (\ell, v_n, t+1, V')\}, T[\pi \mapsto V']) \\ & \text{Thread-UNINITIALIZED} \\ \varepsilon \in \{ \langle \text{Read}, \ell, v \rangle, \langle \text{Update}, \ell, v_o, v_n \rangle \} \\ & T(\pi)(\ell) = \bot \end{array} $ |

| $\overline{(M,T) \xrightarrow{(\operatorname{Fork},\rho)} \pi (M,T[\rho \mapsto T(\pi)])}$                                                                              | $(M, T) \xrightarrow{\epsilon_{\pi}} \bot_{\text{uninit}}$                                                                                                                                                                                         |

**Figure 1** Per-thread reductions for RA without NA.

#### Functional correctness of MP

With the operational semantics of RA, we can now sketch why MP (assuming for now that all its accesses are RA) is functionally correct, *i.e.*, why the read of x by the second thread will return 37 when the program terminates. The write of 37 to x is recorded at a view  $V_{37}$ , which is then included in the view  $V_1$  of the write of 1 to y by the first thread. When the second thread reads 1 from y, its local view is updated to incorporate  $V_1$  (and thus also  $V_{37}$ ). A read from x is now guaranteed to read from the message setting x to 37 or from a more recent one, but no more recent one exists. Consequently, the return value will be 37.

## 2.2 Non-Atomics

Formally, C11 defines a data race as two memory accesses to the same location—of which at least one is a write and at least one is non-atomic—that are not ordered by "happens-before." A program that exhibits data races in *some* of its execution graphs is called racy, and its behavior is considered undefined. We now show how to account for non-atomics and data races in the context of our operational semantics.

Let us first extend the set of physical states by another error state  $\perp_{\text{race}}$ , whose intent is captured by the following correspondence: a program is racy if and only if at least one of its machine executions can reach  $\perp_{\text{race}}$  (stated and proved formally in our appendix [1]).

To detect data races during the execution of a program, we add an additional component to the physical state: the *non-atomic view* N, which tracks the timestamp of the most recent non-atomic write to every location. Then, we place the following restrictions on all atomic and non-atomic operations (if violated, the program will enter the  $\perp_{\text{race}}$  state):

- To perform any access (atomic or non-atomic) to a location  $\ell$ , a thread  $\pi$  must have observed the most recent non-atomic write to  $\ell$ , *i.e.*,  $N(\ell) \leq T(\pi)(\ell)$ .

- A thread  $\pi$  can only perform a non-atomic read from a location  $\ell$  if it has observed the most recent (atomic or non-atomic) write to  $\ell$ , *i.e.*,  $\nexists t$ ,  $(\ell, \_, t, \_) \in M$ .  $T(\pi)(\ell) < t$ .

$$\begin{aligned} & \underset{(\ell, v, t, V) \in M}{(\ell, v, t, V) \in M} & T(\pi)(\ell) \leq t \\ & \underset{(\alpha = na \Rightarrow \forall v', t', V'.(\ell, v', t', V') \in M \Rightarrow t' \leq T(\pi)(\ell)}{(M, T, N) \xrightarrow{(\text{Read}_{\alpha}, \ell, v)} \pi} & (M, T[\pi \mapsto T(\pi) \sqcup V], N) \end{aligned}$$

$$\begin{aligned} & \underset{(M, T, N)}{\overset{(\text{Write}_{at}, \ell, v)}{(Write}_{at}, \ell, v)} \pi & (M, U[\pi \mapsto T(\pi) \sqcup V], N) \end{aligned}$$

$$\begin{aligned} & \underset{(M, T, N)}{\overset{(\text{Write}_{at}, \ell, v)}{(Write}_{at}, \ell, v)} \pi & (M \cup \{(\ell, v, t, V')\}, T[\pi \mapsto V'], N) \end{aligned}$$

$$\begin{aligned} & \underset{(M, T, N)}{\overset{(\text{Write}_{at}, \ell, v)}{(Write}_{at}, \ell, v)} \pi & (M \cup \{(\ell, v, t, V')\}, T[\pi \mapsto V'], N) \end{aligned}$$

$$\begin{aligned} & \underset{(M, T, N)}{\overset{(\text{Write}_{at}, \ell, v)}{(Write}_{at}, \ell, v)} \pi & (M \cup \{(\ell, v, t, V')\}, T[\pi \mapsto V'], N[\ell \mapsto t]) \end{aligned}$$

$$\begin{aligned} & \underset{(\ell, v_o, t, V) \in M}{\overset{(\ell, v_o, t, V) \in M}{(W \cup \{(\ell, v, t, V')\}, T[\pi \mapsto V'], N[\ell \mapsto t])}} \end{aligned}$$

$$\begin{aligned} & \underset{(\ell, v_o, t, V) \in M}{\overset{(\text{Write}_{at}, \ell, v_o, v_n)}{(W \cup \{(\ell, v_n, t + 1, V')\}, T[\pi \mapsto V'], N)} \end{aligned}$$

$$\begin{aligned} & \underset{(K, T, N)}{\overset{(\text{Write}_{at}, \ell, v_o, \tau_n)}{(Write}_{at}, \ell, v_o, (Update, \ell, v_o, v_n)} \ast \underbrace{(K_{T}, N, N) \xrightarrow{(Write}_{at}, \ell, v_o, T(\pi)(\ell) \leq t}{(M, T, N) \xrightarrow{(Write}_{at}, \ell, v_o, T(\pi)(\ell) < t'} \end{aligned}$$

$$\begin{aligned} & \underset{(K, T, N)}{\overset{(Write}_{at}, \ell, v, \tau', V') \in M \land T(\pi)(\ell) < t'}{(M, T, N) \xrightarrow{(Write}_{at}, \ell, v_o, T(\pi)(\ell) < t'} \end{aligned}$$

$$\begin{aligned} & \underset{(K, T, N) \xrightarrow{(Write}_{at}, \ell, v, \tau', V') \in M \land T(\pi)(\ell) < t'}{(M, T, N) \xrightarrow{(Write}_{at}, \ell, v, \tau'}} \end{aligned}$$

In addition to these restrictions, we require non-atomic writes to pick timestamps greater than all existing timestamps of messages of the same location. Intuitively, these restrictions enforce that each non-atomic write to  $\ell$  starts a new "era" in  $\ell$ 's timestamps, after which any attempt to access writes from a previous era (or to write with a timestamp from a previous era) constitutes a race. Note that there is an asymmetry between non-atomic reads and writes: non-atomic writes to  $\ell$  are allowed even when the thread has not observed the most recent write to  $\ell$ , as it is only required to observe the most recent *non-atomic* write to  $\ell$ . One might fear that this fails to detect the case when a non-atomic write is racing with a concurrent atomic write (and the atomic write happens first); but in this case the race will be detected in a different execution where the non-atomic write happens first (and the atomic write enters the  $\perp_{\rm race}$  state), so the program will nevertheless be declared racy.

Revisiting MP, we note that it is safe to have non-atomic accesses to x: the write is performed while the left thread is necessarily aware of the most recent non-atomic write to x (the initialization); and the read is performed while the right thread is necessarily aware of the most recent write to x, whose timestamp was incorporated into the right thread's view when it read y = 1.

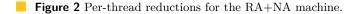

Figure 2 presents the full operational semantics. It is based on the following definition of a physical state.

$$\begin{split} v \in \mathrm{Val} &::= () \mid z \in \mathbb{Z} \mid \ell \in \mathrm{Loc} \mid \mathsf{fix} \ (f, x). \ e \\ \alpha \in \mathrm{Access} ::= \mathrm{at} \mid \mathrm{na} \\ e \in \mathrm{Expr} ::= v \mid e_1 \ e_2 \mid \ \mathsf{if} \ z \ \mathsf{then} \ e_1 \ \mathsf{else} \ e_2 \mid \mathsf{fork} \ e \mid \ell_{[\alpha]} \mid \ell_{[\alpha]} := v \mid \mathsf{cas}(\ell, v, v) \mid \dots \end{split}$$

$$\begin{array}{cccc} \ell_{[\alpha]} & \xrightarrow{\langle \operatorname{Read}_{\alpha}, \ell, v \rangle} & v, \operatorname{nil} \\ \\ \ell_{[\alpha]} := v & \xrightarrow{\langle \operatorname{Write}_{\alpha}, \ell, v \rangle} & (), \operatorname{nil} \\ \\ \operatorname{cas}(\ell, v_o, v_n) & \xrightarrow{\langle \operatorname{Update}, \ell, v_o, v_n \rangle} & 1, \operatorname{nil} \\ \\ \operatorname{cas}(\ell, v_o, v_n) & \xrightarrow{\langle \operatorname{Read}_{\operatorname{at}}, \ell, v \rangle} & 0, \operatorname{nil} & \operatorname{if} v \neq v_o \\ \\ & \operatorname{fork} e & \xrightarrow{\langle \operatorname{Fork}, \rho \rangle} & (), [e] \\ \\ (\operatorname{fix} (f, x). e) v & \rightarrow & e[(\operatorname{fix} (f, x). e)/f][v/x], \operatorname{nil} \\ \\ \operatorname{if} z \operatorname{then} e_1 \operatorname{else} e_2 & \rightarrow & e_1, \operatorname{nil} & \operatorname{if} z \neq 0 \\ \\ & \operatorname{if} z \operatorname{then} e_1 \operatorname{else} e_2 & \rightarrow & e_2, \operatorname{nil} & \operatorname{if} z = 0 \\ \\ & \cdots \end{array}$$

**Figure 3** Main  $\lambda_{\rm RN}$  expressions and expression reductions.

## Definition 2 (Physical State).

Let  $\sigma \in \Sigma \triangleq \left(\mathcal{P}(\text{Msg}) \times (\text{ThreadId} \stackrel{\text{fin}}{\rightharpoonup} \text{View}) \times \text{View}\right) \uplus \{\perp_{\text{race}}, \perp_{\text{uninit}}\}$  represent physical machine states. We write M, T, and N to denote the components of a non-error state. The initial physical state, denoted  $\sigma_{\text{init}}$ , is given by  $(\emptyset, [0 \mapsto \emptyset], \emptyset)$ .

## **2.3** The $\lambda_{\rm RN}$ language

$\lambda_{\text{RN}}$  is a standard lambda calculus with recursive functions, forks, and references with atomic and non-atomic accesses. The **repeat** construct that we have used in MP can be defined in terms of recursive functions. The interesting part of the language and its expression reductions is given in Figure 3. The expression reduction relation  $(e \xrightarrow{\varepsilon} e', \overline{e}_f)$  has four components: the original expression e, an (optional) machine memory event  $\varepsilon$ , the resulting expression e', and a list of newly created threads  $\overline{e}_f$ . Only the rule for **fork** e creates a new thread (*i.e.*, a singleton list [e]), while all other reductions produce an empty list (*i.e.*, nil).

The per-thread language reductions ( $\sigma; e \xrightarrow{\varepsilon} \pi \sigma'; e', \overline{e}_f$ ) are then the combination of the expression reductions and the machine reductions, given by the COMBINED-\* rules in Figure 4. Non-stateful reductions (COMBINED-PURE) simply defer to the expression reductions, while stateful reductions (COMBINED-MEM and COMBINED-FORK) use the event label  $\varepsilon$  and the thread id  $\pi$  to tie the expression and machine reductions together correctly. These per-thread reductions then are lifted in a straightforward manner to the full (threadpool) reductions.

## 3 Iris

Iris is a generic framework for constructing concurrent separation logics. One can instantiate the framework with any language that has an operational interleaving semantics, and then easily derive time-tested reasoning principles for one's target logic, including various "protocol" mechanisms for controlling interference. Figure 5 provides an excerpt of Iris syntax.

Iris supports the common connectives (False, True,  $\Rightarrow$ ,  $\land$ ,  $\lor$ , =,  $\exists$ ,  $\forall$ ,  $\mu$ ) and proof rules standard in higher-order separation logics. Iris's extended set of constructs includes physical state ownership Phys( $\sigma$ ), ghost state ownership  $[\overline{a}]^{\gamma}$ , the later  $\triangleright$  and always  $\Box$  modalities,

**Figure 4** Threadpool reductions.

$$\begin{split} P &::= \mathsf{False} \mid \mathsf{True} \mid P \Rightarrow Q \mid P \land Q \mid P \lor Q \mid P \ast Q \mid P \twoheadrightarrow Q \mid \exists x. \ P \mid \forall x. \ P \mid \mu x. \ P \\ &\mid \mathsf{Phys}(\sigma) \mid \begin{bmatrix} a \end{bmatrix}^{\gamma} \mid \triangleright P \mid \Box P \mid \boxed{P}^{\mathcal{N}} \mid P^{\mathcal{N}_1} \Rrightarrow^{\mathcal{N}_2} Q \mid \{P\} \ e \ \{x. \ Q\}_{\mathcal{N}} \mid \dots \end{split}$$

**Figure 5** An excerpt of Iris syntax.

invariants  $\mathbb{P}^{\mathcal{N}}$ , view shifts  $P^{\mathcal{N}_1} \Rightarrow \mathcal{N}_2 Q$ , and Hoare triples  $\{P\} e \{x, Q\}_{\mathcal{N}}$ . We will first explain these constructs via a running example, in which we use Iris to verify the MP example in a simple, sequentially consistent language called  $\lambda_{SC}$ . This will not only illustrate how one can derive within Iris a target logic for a language defined by an operational semantics, but will also serve as a warm-up for our subsequent explanation of how we can instantiate Iris to reason about weak memory.

## Road map

The process of instantiating Iris to derive new logics follows a simple pattern, which is worth articulating up front:

- 1. When we first instantiate Iris, the only primitive assertion we get about the state of the program is the *physical state ownership* assertion  $\mathsf{Phys}(\sigma)$ , which asserts that  $\sigma$  is the current global state of the machine. Together with this assertion we also get for free a bunch of *large-footprint* specifications for the primitive commands of the language, based directly on their operational semantics. For example, the primitive specification we get for updating a location in  $\lambda_{SC}$  will be  $\{\mathsf{Phys}(\sigma)\} \ \ell := v \ \{\mathsf{Phys}(\sigma[\ell \mapsto v])\}$ .

- 2. Of course, one of the main points of separation logic is to be able to reason modularly using *local* assertions about the machine state, such as the *points-to* assertion,  $\ell \to v$ , and correspondingly give *small-footprint* specifications of the primitive commands, such as  $\{\ell \to w\} \ \ell := v \ \{\ell \to v\}$ . In Iris, such local assertions are not baked into the logic, but rather are encodable using *ghost state ownership* assertions, and the user of the logic has a great deal of flexibility concerning how these assertions are defined. In the case of the points-to assertion,  $\ell \to v$ , we will define this assertion so as to represent the *knowledge* that  $\ell$  currently points to v and the *rights* to read and write  $\ell$ .

- **3.** On its own, a local, user-defined ghost state assertion like the points-to assertion is merely a *representation* of knowledge and rights. In order to give meaning to such a ghost state assertion—*i.e.*, to make sure it is in sync with the primitive physical state assertion—we

$$\begin{array}{rcl} (!\ell,\sigma) & \to & (v,\sigma) & \text{ if } \sigma(\ell) = v \\ (\ell := v,\sigma) & \to & ((),\sigma[\ell \mapsto v]) & \text{ if } \ell \in \operatorname{dom}(\sigma) \end{array}$$

**Figure 6** Main heap-related reductions of the  $\lambda_{SC}$  language.

establish an *invariant* tying the assertions together. In the case of the points-to assertion, this invariant will enforce that when a thread owns the ghost state assertion  $\ell \hookrightarrow v$ , its "knowledge" that  $\ell$  currently points to v in the physical machine state is actually correct.

In short, ghost state assertions represent local knowledge and rights concerning the machine state, and *invariants enforce* that ghost state assertions mean what they say they mean.

## 3.1 Iris by Example

Our example programming language  $\lambda_{SC}$  is a standard lambda calculus with references. It is basically the same as  $\lambda_{RN}$ , except that all accesses are sequentially consistent, and races are permitted (they do not induce stuckness). The language's physical state is a heap  $\sigma$ , which is a finite map from allocated locations to values. The main heap-related reductions of  $\lambda_{SC}$  are given in Figure 6. When we instantiate Iris with  $\lambda_{SC}$ 's operational semantics, (as explained in the above road map) what we get automatically from Iris are the following *large-footprint* Hoare triples concerning the physical state ownership assertion Phys( $\sigma$ ):

| Phys-Heap-Read                                                             | Phys-Heap-Write                                                |

|----------------------------------------------------------------------------|----------------------------------------------------------------|

| $\{Phys(\sigma) * \sigma(\ell) = v\} ! \ell \{z. \ z = v * Phys(\sigma)\}$ | $\{Phys(\sigma)\}\ \ell := v\ \{Phys(\sigma[\ell\mapsto v])\}$ |

Note that z in the first triple binds the return value of the expression  $!\ell$ . In the second triple, the expression returns the unit value, so we elide the binder.

## 3.1.1 Encoding Separation Logic for $\lambda_{SC}$

We would now like to encode these *small-footprint* Hoare triples for  $\lambda_{SC}$ :

| Heap-Read                                                                         | Heap-Write                                                            |

|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| $\{\ell \hookrightarrow v\} \ !\ell \ \{z. \ z = v \ast \ell \hookrightarrow v\}$ | $\{\ell \hookrightarrow w\} \ \ell := v \ \{\ell \hookrightarrow v\}$ |

The first step is to define the points-to assertion,  $\ell \hookrightarrow v$ , using Iris's *ghost state*.

#### Ghost state and partial commutative monoids

Ghost state is non-physical state that is only used as part of a program verification but is not itself part of the machine state. In Iris, ghost state is formalized using partial commutative monoids (PCMs).<sup>3</sup> The assertion  $[a:M]^{\gamma}$  asserts the ownership of the ghost resource *a* for an instance  $\gamma$  of the PCM *M*. Separating conjunction for ghost state assertions simply lifts the PCM composition operation to the assertion level:  $[a:M]^{\gamma} * [b:M]^{\gamma} \iff [a:M]^{\gamma} \in [a:M]^{\gamma}$ . If two PCM fragments are not compatible (i.e. their composition is not defined), then it is

<sup>&</sup>lt;sup>3</sup> Actually, ghost state in Iris is based on the more general mechanism of "cameras" (aka step-indexed resource algebras), which can support a more general form of higher-order ghost state [13].

#### 17:12 Strong Logic for Weak Memory

not possible to own both of them at the same time, *i.e.*, if  $a \cdot b = \bot$  then  $[a]^{\gamma} * [b]^{\gamma} \Rightarrow \mathsf{False}^4$ In order to maintain consistency of the logic, therefore, changes to ghost state are restricted to *frame-preserving* updates, in which a PCM fragment *a* can only be updated to *b* if *b* preserves compatibility with any other fragments in the environment (the *frame*):

$$\frac{\forall a_f. \ a \cdot a_f \neq \bot \Rightarrow b \cdot a_f \neq \bot}{|a_!^{-\gamma} \Rightarrow |b_!^{-\gamma}}$$

Ghost updates belong to the set of *logical computations*, or in Iris terminology, view shifts. A view shift  $P \Rightarrow Q$  represents the capability of transforming a resource satisfying P into a resource satisfying Q without changing the physical state.

## A PCM for heaps

As a step towards defining  $\ell \hookrightarrow v$ , let us now construct a PCM called HEAP that has the same basic structure as the physical heap, but allows splitting and recomposition. (We will ultimately need a slightly more sophisticated PCM to define  $\ell \hookrightarrow v$ , but HEAP is an important part of the construction.) HEAP is a finite partial map from locations to values, with the empty heap as its unit element, and the composition on heaps is defined as disjoint union (*i.e.*, union if the heaps have disjoint domain, and undefined otherwise). The composition implies that the singleton heap  $[\ell := v]$  does not combine with itself, so it can only be uniquely owned, and it also represents the permission required to update  $\ell$ :

$$\begin{array}{lll} & \text{Ghost-Heap-Exclusive} & \text{Ghost-Heap-Update} \\ & \left[\left[\ell:=v\right]\right]^{\gamma} * \left[\left[\ell:=w\right]\right]^{\gamma} \vdash \mathsf{False} & \left[\left[\ell:=w\right]\right]^{\gamma} \Rrightarrow \left[\left[\ell:=v\right]\right]^{\gamma} \end{array} \right. \end{array}$$

The singleton heap  $[\ell := v]$  therefore has the desired properties for defining the local assertion  $\ell \to v$ , but unfortunately it is still not quite enough: we also need some way to tie this ghost state assertion to the underlying physical state of the program. Toward this end, we employ Iris's *invariants*.

## Invariants

Invariants in Iris can be thought of as assertions that hold of *some* shared resource at all times, although the choice of which shared resource satisfies them is allowed to vary over time. The Iris invariant assertion  $\mathbb{P}^{\mathcal{N}}$  stipulates that P is an invariant. The resource that satisfies it is shared with all threads, and thus any thread can access it freely in a single physical step<sup>5</sup>: it can *open* the invariant and gain local ownership of the resource for the duration of the operation, so long as it can *close* the invariant by relinquishing ownership of some (potentially different) resource satisfying P at the end of the operation. For bookkeeping purposes—specifically, to ensure that we do not unsoundly open the same invariant more than once in a nested fashion—invariants in Iris are named, and the  $\mathcal{N}$  in the above invariant assertion is a *namespace* (set of names) from which the name of the invariant must come.

Invariants belong to the set of *persistent* assertions, denoted with the always modality  $\Box$ . The assertion  $\Box P$  establishes the *knowledge* that P holds without any ownership, and

<sup>&</sup>lt;sup>4</sup> In the rest of the paper we also suppress the PCM M in  $[a:M]^{\gamma}$  when it can be inferred in context.

<sup>&</sup>lt;sup>5</sup> In Iris terminology, a resource in an invariant can be accessed within an *atomic* operation, which is an operation that takes only a single physical step of execution. We do not use the term here to avoid confusion with C11 atomics.

therefore holds forever after. Putting resources into an invariant is thus a common way to share or transfer ownership through the use of freely distributable knowledge.

Meanwhile, the actions of opening and closing invariants belong to the set of logical computations, or view shifts. To account for invariants, view shifts are extended with namespaces as well:  $P^{\mathcal{N}_1} \Rightarrow \mathcal{N}_2 Q$  asserts that, assuming the invariants named in  $\mathcal{N}_1$  hold before the view shift, then the invariants named in  $\mathcal{N}_2$  hold after the view shift. Opening and closing of invariants are then formalized as follows:

$$\begin{array}{ccc} \text{Inv-OPEN} & & \text{Inv-CLOSE} \\ \hline P^{\mathcal{N}} \vdash \mathsf{True}^{\mathcal{N}} \Rightarrow^{\emptyset} P & & \hline P^{\mathcal{N}} \vdash P^{\emptyset} \Rightarrow^{\mathcal{N}} \mathsf{True} \end{array}$$

INV-OPEN allows a thread to open the invariant  $\mathbb{P}^{\mathcal{N}}$  and gain ownership of P but prevents it from doing so more than once. Only after applying INV-CLOSE and re-establishing the invariant will the thread be able to open it again.

**Note:** The INV-OPEN rule as stated here is only sound if P talks about ownership (of physical or ghost state) and not about the existence of other invariants. In general, however, Iris makes no such restriction; rather, it supports *impredicative invariants*, meaning that P can be an arbitrary assertion. In order to avoid paradoxes caused by impredicative circularities (like the one described in [16]), the fully general version of this rule in Iris requires that P be guarded by the step-indexed *later* modality ( $\triangleright$ ). Fortunately, in most cases the  $\triangleright$ 's can be stripped away automatically (the Iris proof mode in Coq provides support for doing this) and do not play an interesting role in proofs. To focus the presentation of this paper, we will therefore suppress further discussion of the  $\triangleright$  modality.

Hoare triples in Iris are also annotated with invariant namespaces, since Hoare triples combine both physical and logical computations. A Hoare triple  $\{P\} \ e \ \{x.\ Q\}_{\mathcal{N}}$  with a namespace  $\mathcal{N}$  implies that if the invariants in  $\mathcal{N}$  hold before the expression's execution, then they will be preserved between every step and also after its execution. Consequently, when verifying any single physical step of computation, we are free to open the invariants in  $\mathcal{N}$  so long as we immediately close them. This reasoning is encapsulated in the following "atomic rule of consequence":

$$\frac{P \stackrel{\mathcal{N} \uplus \mathcal{N}'}{\Rightarrow} \stackrel{\mathcal{N}}{\Rightarrow} P' \qquad \{P'\} e \{v. Q'\}_{\mathcal{N}} \qquad \forall v. Q' \stackrel{\mathcal{N} \Longrightarrow \mathcal{N} \uplus \mathcal{N}'}{\Rightarrow} Q \qquad e \text{ takes 1 physical step}}{\{P\} e \{v. Q\}_{\mathcal{N} \uplus \mathcal{N}'}}$$

Since bookkeeping of namespaces is largely a tedious detail (and one which Coq will force us to get right), we will for the remainder of the paper suppress namespaces from definitions and proofs. We will always use disjoint namespaces to ensure correctness in opening invariants.

#### Linking physical and ghost state using invariants and the "authoritative" PCM

Now, returning to our example, the key idea is to use an invariant to tie the physical state assertion together with local ghost state assertions, thereby giving them meaning. To achieve this, we will employ an extremely useful construction called the *authoritative* PCM [14].

Given a base PCM  $\mathcal{M}$ , the authoritative PCM AUTH( $\mathcal{M}$ ) has two types of elements: authoritative • *a* and non-authoritative • *a* (for  $a \in \mathcal{M}$ ). For any instance  $\gamma$ ,  $[\bullet a]^{\gamma}$  is *exclusive*  $(i.e., [\bullet a]^{\gamma} * [\bullet a]^{\gamma} \vdash \mathsf{False})$ , and is the main point of reference for all the non-authoritative fragments, in the sense that any ownable fragment  $[\bullet b]^{\gamma}$  must have *b* included in *a*, that is  $\exists c. a = b \cdot c$ . The PCM's update therefore requires more: if one wants to update *b* to *b'*, it

#### 17:14 Strong Logic for Weak Memory

has not only to ensure b' is compatible with c, but also has to update a to  $a' = b' \cdot c$ . These properties are summarized in the following two rules:

With these two rules in hand, we can derive the following rules for operations on AUTH(HEAP):

We are now ready to establish the invariant  $\exists \sigma$ .  $\mathsf{Phys}(\sigma) * [\bullet \sigma]^{\gamma}$ , which binds together the physical state ownership and the authoritative ghost heap ownership. With the invariant in place, AGHOST-HEAP-AGREE implies that if a thread owns the singleton ghost heap  $[\circ [\ell := v]]$ locally, then, in combination with the invariant, it is guaranteed that  $\ell$  currently has value vin the physical heap. AGHOST-HEAP-EXCLUSIVE and AGHOST-HEAP-UPDATE ensure that only the one thread who owns  $[\circ [\ell := v]]^{\gamma}$  can make updates to the contents of  $\ell$ .

The points-to assertion is then defined as  $\ell \hookrightarrow v \triangleq \left[ \circ [\ell := v] \right]^{\gamma}$ , and we can easily prove the small-footprint triples from the beginning of this section by combining the above rules for authoritative ghost heaps with those for opening and closing invariants.

## 3.1.2 Verifying MP in $\lambda_{\rm SC}$

Using the small-footprint triples, we are ready to verify MP in  $\lambda_{SC}$ . We discuss the proof in a bit of detail here, since later on we will show how to adapt this proof to verify MP under weak-memory semantics.

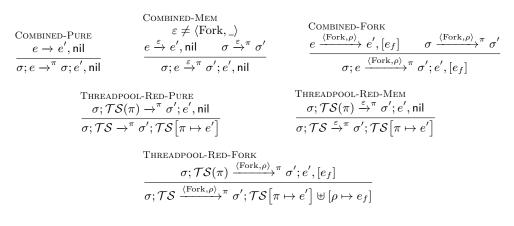

The proof of MP is given in Figure 7. As a proof convention, we only mention persistent assertions (like invariants) once and use them freely later, since they are always true after being established. The proof works essentially as follows.

First of all, both threads want to operate on y simultaneously, so we need to put ownership of y into an invariant  $\boxed{\text{Inv}_y}$ . This invariant says that y is in one of two states—0 or 1. We can establish the invariant right after the initialization of y (the write of 0 to y), because y is in state 0 at that moment. The first thread is responsible for setting y to state 1. When the second thread observes that y is in state 1, it will expect to be able to gain ownership of  $x \hookrightarrow 37$ . To achieve this, in state 1,  $\text{Inv}_y$  asserts the existence of another invariant  $\boxed{\text{Inv}_x}$ concerning x, and it is this latter invariant that we use to transfer ownership of location xfrom the first thread to the second thread.

To understand  $\operatorname{Inv}_x$ , it helps to have seen the film *Raiders of the Lost Ark*, or at least the first few minutes of it, in which Indiana Jones (played by Harrison Ford) attempts to steal a precious golden idol from an ancient Peruvian temple—without setting off booby traps—by swapping it for a similarly weighted bag of sand. Unfortunately for him, the temple detects his ruse and tries to kill him. But we can play a similar trick, and Iris will be perfectly happy! In our case, the "golden idol" is  $x \hookrightarrow 37$ , which is transferred into the invariant  $\operatorname{Inv}_x$  when it is established by the first thread. The "bag of sand" is a "token" [ $\stackrel{\frown}{\diamond}$ ] (a uniquely ownable piece of ghost state) that is given to the second thread at the beginning of its execution. Inv<sub>x</sub> simply asserts that it owns either the golden idol or the bag of sand. Thus, when the

$$\begin{array}{c} Invariants: \\ Inv_y \triangleq y \hookrightarrow 0 \lor y \hookrightarrow 1 \ast [Inv_x] \\ Inv_x \triangleq [\overbrace{\bigcirc}^{-} \lor x \hookrightarrow 37 \end{array} \end{array} \begin{array}{c} \left\{ \begin{array}{c} x \hookrightarrow 0 \ast [Inv_y] \right\} \\ x := 37 \\ \left\{ x \hookrightarrow 37 \right\} \\ \left\{ Inv_x \right\} \\ \left\{ Inv_x \right\} \\ \left\{ y \hookrightarrow - \right\} \\ y := 1 \\ \left\{ y \hookrightarrow 1 \ast [Inv_x] \right\} \\ \left\{ x \hookrightarrow 37 \right\} \\ x \hookrightarrow 37 \end{array} \right\} \\ \left\{ x \hookrightarrow 37 \\ x \hookrightarrow 37 \\ x \hookrightarrow 37 \\ \left\{ z. \ z = 37 \ast x \hookrightarrow 37 \right\} \\ \left\{ z. \ z = 37 \ast x \hookrightarrow 37 \right\} \end{array} \right\}$$

Ш

second thread learns of the existence of  $\text{Inv}_x$ , it can safely use the invariant opening and closing rules to swap the bag of sand in its possession for the golden idol owned by  $\text{Inv}_x$ , and thereafter claim local ownership of  $x \hookrightarrow 37$ .

## 3.2 Instantiating Iris with $\lambda_{\rm RN}$

We now consider an instantiation of Iris with our  $\lambda_{\rm RN}$  language from Section 2.3. A key difference between  $\lambda_{\rm RN}$  and  $\lambda_{\rm SC}$  is that the expression reductions of  $\lambda_{\rm SC}$  do not depend on which thread is executing the expression, since every thread has the same global view of the memory, whereas the reductions of  $\lambda_{\rm RN}$  depend on the current thread's subjective view of the memory. Thus, we need to be able to talk about thread ids in our logic as well. To this end, we pair up expressions from  $\lambda_{\rm RN}$  with thread ids, making them visible in our specifications. Eventually, in Section 4, we will see how we can reason about  $\lambda_{\rm RN}$  without talking explicitly about thread ids.

## 3.2.1 Encoding Separation Logic for $\lambda_{\rm RN}$

After instantiating Iris with  $\lambda_{\rm RN}$ , as in the case of  $\lambda_{\rm SC}$ , Iris provides us with large-footprint specifications of the primitive commands for free, which concern the physical state assertion and mirror the rules of  $\lambda_{\rm RN}$ 's operational semantics. Recall that in  $\lambda_{\rm RN}$  the physical state is a tuple (M, T, N) of the message pool M, the current view map T, and the non-atomic timestamp map N. As before, we aim to develop "local" assertions using ghost state, establish an invariant that connects those local assertions to the physical state assertion, and then derive small-footprint specifications of the primitive commands for use in modular verification. But what kind of "local" assertions do we want?

For  $\lambda_{SC}$ , we had the points-to assertion  $\ell \hookrightarrow v$ , but in  $\lambda_{RN}$  we no longer have a simple mapping from locations to values. Rather, associated with each location  $\ell$  is a set of messages corresponding to writes to  $\ell$ . We will represent that associated information as a *history* h, consisting of a set of triples (v, t, V), where v is a value written to  $\ell$ , t is the timestamp at which that value was written, and V is the view of the writing thread at the time the write occurred. Note that V incorporates the new timestamp, *i.e.*,  $V(\ell) = t$ . To reflect the per-location history, we define our first local assertion: The *history ownership* assertion Hist $(\ell, h)$  asserts ownership of  $\ell$  and knowledge of its write history h.

Since the ability to read or write values in  $\lambda_{\rm RN}$  depends on threads' local views of memory, we would also like to support an assertion of *thread-view ownership*, Seen $(\pi, V)$ , which asserts ownership of the current view V of the thread  $\pi$  and is required to update  $\pi$ 's view. Since any operation by a thread  $\pi$  on a location  $\ell$  relies on both  $\pi$ 's current view and  $\ell$ 's history, the

#### 17:16 Strong Logic for Weak Memory

BA

$\operatorname{Hist}(\ell, h) \triangleq \left[\circ \left[\ell := h\right]\right]^{\gamma_1}$  $\operatorname{Seen}(\pi, V) \triangleq \left[ \circ \left[ \pi := V \right] \right]^{\gamma_2}$  $\mathsf{PSInv} \triangleq \exists \sigma. \exists H \in \operatorname{Loc} \stackrel{\operatorname{fin}}{\rightharpoonup} \mathcal{P}(\operatorname{Val} \times \operatorname{Time} \times \operatorname{View}). \mathsf{Phys}(\sigma) * [\bullet H_1^{\gamma_1} * [\bullet \sigma. T_1^{\gamma_2} * \mathsf{HInv}(\sigma, H)]$  $\mathtt{HInv}(\sigma, H) \triangleq \mathrm{dom}(H) = \{m.\ell \mid m \in \sigma.M\} \land (\forall m \in \sigma.M. \ m.t = m.V(m.\ell))$  $\land \forall \ell \in \operatorname{dom}(H). \ H(\ell) = \{(m.v, m.t, m.V) \mid m \in \sigma. M \land m.\ell = \ell \land m.t \ge \sigma. N(\ell)\}$

**Figure 8** Ghost state and invariant setup for  $\lambda_{\rm RN}$ .

$$\begin{split} & \underset{[\texttt{PSInv}]}{\text{PSInv}} \vdash \{ \operatorname{Seen}(\pi, V) * \operatorname{Hist}(\ell, h) * \operatorname{init}(h, V) * \operatorname{na}(h, V) \} \\ & \ell_{[\operatorname{na}]}, \pi \\ & \{v. \operatorname{Seen}(\pi, V) * \operatorname{Hist}(\ell, h) * \operatorname{na}(h, V) * \operatorname{max}(h).v = v \} \end{split} \\ & \underset{[\texttt{PSInv}]}{\text{Base-NA-WRITE}} \vdash \{ \operatorname{Seen}(\pi, V) * \operatorname{Hist}(\ell, h) * \operatorname{alloc}(h, V) \} \\ & \ell_{[\operatorname{na}]} := v, \pi \\ & \{ \exists V' \sqsupseteq V, t, h' = \{(v, t, V')\}. \operatorname{Seen}(\pi, V') * \operatorname{Hist}(\ell, h') * \operatorname{na}(h', V') * \operatorname{init}(h', V') \} \end{split} \\ & \underset{[\texttt{PSInv}]}{\text{Base-AT-READ}} \vdash \{ \operatorname{Seen}(\pi, V) * \operatorname{Hist}(\ell, h) * \operatorname{init}(h, V) \} \\ & \ell_{[\operatorname{at}]}, \pi \\ & \{ v. \exists t_1, V_1, V' \sqsupseteq V \sqcup V_1. \operatorname{Seen}(\pi, V') * \operatorname{Hist}(\ell, h) * (v, t_1, V_1) \in h * t_1 \geq V(\ell) \} \end{aligned}$$

\\ & \underset{[\texttt{PSInv}]}{\text{Base-AT-WRITE}} \vdash \{ \operatorname{Seen}(\pi, V) \* \operatorname{Hist}(\ell, h) \* \operatorname{alloc}(h, V) \} \\ & \ell\_{[\operatorname{at}]} := v, \pi \\ & \{ \exists V' \sqsupseteq V, t, h' = h \uplus \{(v, t, V')\}. \operatorname{Seen}(\pi, V') \* \operatorname{Hist}(\ell, h') \* \operatorname{init}(h', V') \} \end{split}

**Figure 9** Selected Hoare triples of  $\lambda_{\rm RN}$  base logic.

pair of history and thread-view ownership assertions comprise the general ghost ownership required for accessing the location.

To the these local assertions to the global physical state, we use a construction very similar to the one for  $\lambda_{\rm SC}$ . The local assertions are defined as before by wrapping finite-map PCMs with the authoritative PCM construction, and the invariant enforces that these ghost maps are coherent with the physical state. The definitions of the invariant PSInv and the two local assertions are given in Figure 8. The  $\operatorname{Hist}(\ell, h)$  and  $\operatorname{Seen}(\pi, V)$  assertions also have the exact same rules for exclusiveness, agreement, and updating as the  $\ell \hookrightarrow v$  assertion of  $\lambda_{SC}$ .

It is important to note that the history ownership assertion  $\operatorname{Hist}(\ell, h)$  does not record the full history of  $\ell$ , but only write events of the *current era* (see Section 2.2), *i.e.*, only events as recent as or more recent than the last non-atomic write to  $\ell$ . This is reflected in the last condition of HInv:  $m.t \ge \sigma.N(\ell)$ . Defining  $\text{Hist}(\ell, h)$  this way helps to simplify the job of the user of the logic in establishing the absence of races: by construction, it is impossible to even attempt to read (racily) from write events before the current era. In order to preserve this property of Hist $(\ell, h)$ , a non-atomic write  $(v_{na}, t_{na}, V_{na})$  must completely remove all write events currently in h (which would be racy to access now), and replace it with a new history h' that contains only the newly created non-atomic write event:  $h' = \{(v_{na}, t_{na}, V_{na})\}$ .

With the physical state shared and its ghost counterpart splittable, we are ready to derive the small-footprint Hoare triples, which constitute a base logic that is powerful enough to verify programs in  $\lambda_{\rm RN}$ . A selected set of these triples is given in Figure 9. The general pattern of these rules is that a thread  $\pi$  needs to own the history h of a location  $\ell$  and its own thread view V in order to operate on  $\ell$ . Additionally,  $\pi$  needs to show certain relations between h and V in order to guarantee the safety of its operations. These relations are represented by the alloc, init, and na predicates. The  $\operatorname{alloc}(h, V)$  predicate (resp.  $\operatorname{init}(h, V)$ ) asserts that V has observed an event in h which ensures that  $\ell$  is allocated (resp.  $\operatorname{initialized}$ ). The  $\operatorname{na}(h, V)$  predicate asserts that V has observed the *mo*-latest write event of h, which is needed to do a non-atomic read. Note that all of these predicates require that V has seen *some* event from h—*i.e.*, an event from the current era of  $\ell$ —which, as discussed above, is a prerequisite for non-raciness.

These base logic rules provide a very concise explanation of  $\lambda_{\text{RN}}$ 's operational semantics. BASE-AT-READ, for example, requires the current view's knowledge of  $\ell$  being initialized and ensures that the new updated view V' is at least the join of the local view V and the view  $V_1$ of the write event that the thread reads from. This event must be from h and not *mo*-earlier than the write event observed by the thread previously. BASE-NA-READ is similar, except that it requires that the current view must have observed the *mo*-latest write event to  $\ell$ , and therefore reads from that write event, which we denote by  $\max(h)$ . BASE-NA-WRITE preserves the HInv invariant by proactively dropping from the history all the old write events, which are *mo*-before this non-atomic write. Notice that, unlike BASE-NA-READ, BASE-NA-WRITE does not require na(h, V), as explained in Section 2.2.

## 3.2.2 MP in $\lambda_{\rm RN}$

We show that the base logic is enough to verify MP in  $\lambda_{\rm RN}$ . The invariants and the proof, given in Figure 10, follow closely those used for MP in  $\lambda_{\rm SC}$ . The singleton heap ownership in  $\lambda_{\rm SC}$  is replaced with the history ownership, and extra conditions on view extension are added to reflect the view updates inherent in  $\lambda_{\rm RN}$ . More specifically, in  $\operatorname{Inv}_y$ , we enforce that any write of a non-zero value<sup>6</sup> to y be at a view  $V_1$  that extends  $V_{37}$ , which is the view at which the write of 37 to x is made by the first thread. Consequently, when the second thread observes  $V_1$  (by reading y to be non-zero), it must have also observed  $V_{37}$ , and thus can read x = 37, using the Indiana Jones invariant  $\operatorname{Inv}_x$ . The extra conditions on  $V_0$  ensure that y is initialized with 0 at  $V_0$ , so that the second thread (having observed  $V_0$ ) can safely read y.

We have shown that the base logic is powerful enough to verify MP in  $\lambda_{\rm RN}$ , and in principle it is powerful enough to verify many other realistic weak memory programs that are expressible in  $\lambda_{\rm RN}$  as well. However, it is also clear that the base logic is not abstract enough: one has to burden oneself with keeping track of the low-level details of changes to locations' histories and threads' views. What we really want is a way of abstracting away from those low-level details and finding simple high-level reasoning principles for  $\lambda_{\rm RN}$ , the type of reasoning principles supported by RA+NA logics like GPS and RSL. We will now see how such high-level principles can in fact be derived on top of our low-level base logic.

<sup>&</sup>lt;sup>6</sup> In the MP example this value is always 1.

Invariants:

$\operatorname{Inv}_{y}(V_{0}) \triangleq \exists h. \operatorname{Hist}(y,h) * (0,\_,V_{0}) \in h * \forall V_{1}, v_{1} \neq 0. (v_{1},\_,V_{1}) \in h \Rightarrow \exists V_{37} \sqsubseteq V_{1}. \overline{[\operatorname{Inv}_{x}(V_{37})]}$  $\operatorname{Inv}_{x}(V_{37}) \triangleq \overline{[\diamond_{1}^{\vee} \lor} \operatorname{Hist}(x, [(37,\_,V_{37})])$

Thread 1 proof outline:

Thread 2 proof outline:

$\begin{cases} \operatorname{Seen}(\pi, V_0) * \overline{[\operatorname{Inv}_y(V_0)]} * \overline{[\diamond]} \\ \text{repeat } y_{[\operatorname{at}]}; \\ \exists V_1, V_{37}, V_2. V_2 \sqsupseteq V_1 \sqsupseteq V_{37} * \operatorname{Seen}(\pi, V_2) * \overline{[\operatorname{Inv}_x(V_{37})]} * \overline{[\diamond]} \\ \operatorname{Seen}(\pi, V_2) * V_{37} \sqsubseteq V_2 * \operatorname{Hist}(x, [(37, \_, V_{37})]) \\ x_{[\operatorname{na}]} \\ \{z. \operatorname{Seen}(\pi, V_2) * z = 37 * \operatorname{Hist}(x, [(37, \_, V_{37})]) \} \end{cases}$

**Figure 10** Verification of MP in  $\lambda_{\rm RN}$  base logic.

## 4 iGPS

Vafeiadis *et al.* have introduced several logics for C11, and two in particular that were focused on RA+NA: GPS [33] and RSL [34]. The key difference between these logics and the RA+NA base logic presented in Section 3.2.1 is that, in GPS and RSL, the user does not reason explicitly about views—instead, the assertions of these logics are *implicitly* predicated over the view of the thread asserting them. This helps to hide much tedious reasoning about views, and leads naturally to a model of assertions as predicates over views (Section 4.3).

We have encoded iGPS and iRSL, variants of both GPS and RSL, in Iris, and we will focus here on iGPS, since it is the more sophisticated of the two logics. (We briefly describe iRSL in Section 5.) GPS introduced several useful abstractions that were not present in RSL: PCM-based ghost state, single-location protocols, and escrows. In encoding GPS in Iris, as noted in the introduction, we get PCM-based ghost state completely for free, just by working in Iris. Below, we will describe the other features, and how we account for them in Iris.

Note that our goal with iGPS is not to slavishly imitate all details of GPS, but to provide proof rules very similar to GPS's that are both strong enough to support all the examples from the GPS papers [33, 31] and significantly easier to prove sound within Iris. To this end, we slightly restrict select rules, but only in a way that does not impact their utility on known case studies. We discuss the differences from the original rules in detail in Section 6. Furthermore, in Section 4.2, we show how iGPS supports an additional feature—*single-writer protocols*—that was not supported by the original GPS and that significantly simplifies proofs.

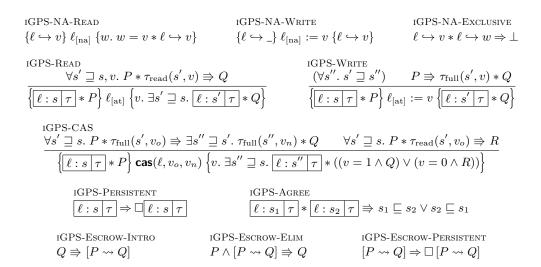

**Figure 11** iGPS proof rules for non-atomics, protocols, and escrows.

## 4.1 Key Features of GPS

In this section, we explain the key features of GPS and how they are formalized in iGPS (besides PCM-based ghost state, which is directly imported into iGPS from Iris). A selected set of iGPS proof rules is given in Figure 11.

## Non-atomics

Since non-atomic locations may not be raced on, GPS (and iGPS) reason about them much in the same way that locations are reasoned about in standard separation logic: using the points-to assertion,  $\ell \hookrightarrow v$ . Note that the proof rules for reading (IGPS-NA-READ) and writing (IGPS-NA-WRITE) and the exclusivity property (IGPS-NA-Exclusive) are equivalent to those from the logic for  $\lambda_{SC}$  (Section 3.1.1). Additionally, GPS (and iGPS) support fractional ownership of non-atomics to allow such locations to be read (but not written) by multiple threads at once. We omit the rules of fractional ownership for brevity.

## Protocols

To reason about RA atomics, we need a mechanism for controlling interference on such accesses. Toward this end, CSLs for SC have supported a variety of *protocol* mechanisms, which control how shared state may evolve over time, and several of the more recent logics [32, 30, 23] employ *state transition systems* (STSs) to formalize such protocols. Crucially, protocols enforce *irreversibility*: the state of an STS protocol can only make forward progress over the course of a proof. For example, in Section 3.1.2, a protocol could enforce that the variable y could only progress from 0 to 1 but not back again. (We did not need to enforce that property to verify the MP example, but it is useful to be able to in general.) In Iris, protocols are encoded using a combination of invariants and ghost state.

Under weak memory, invariants and protocols are unsound in general because they require a single coherent history of updates to all locations. GPS showed how to partially restore protocol reasoning for weak memory with *single-location protocols*: protocols which restrict the evolution of a single shared location. Intuitively, single-location protocols are sound due

## 17:20 Strong Logic for Weak Memory

to the per-location coherence property of C11 (often called "SC per location"): the writes to any single location are totally ordered (by mo). In particular, they maintain the invariant that the order of protocol states associated with writes is consistent with their timestamp (mo) order. If write event x to location  $\ell$  with associated protocol state  $s_x$  is mo-before write event y (to the same location) with protocol state  $s_y$ , then  $s_x$  will be before  $s_y$  in protocol order. Thus, once a thread has observed that the protocol on  $\ell$  has reached state  $s_x$ , it can from that point on only observe the protocol on  $\ell$  to be in states that are accessible from  $s_x$ . This fulfills the expectation that protocol transitions are irreversible.

GPS protocols come equipped with an interpretation predicate which specifies the resources held by the protocol depending on the protocol's state and the location's value. The primitive operations on an atomic location serve to transfer resources in and out of its protocol:

- Writes may transfer resources into the protocol, but may not transfer anything out.

- Reads may not transfer any resources into the protocol, but they may transfer "knowledge" (*i.e.*, duplicable resources) out of it. They are restricted to transferring out duplicable resources because there may be many reads of the same write event.

- Updates (RMWs), by virtue of the physical synchronization they provide, may transfer resources both in and out of the protocol.

In iGPS, we represent protocols in a slightly different way, using *two* interpretations: a "full" interpretation, and a duplicable "read" interpretation that is implied by the full interpretation. The intuition is that the read interpretation is used for reads (since they may only transfer duplicable resources out of the protocol) and the full interpretation is used for the other operations.

We will now present the formal definition of protocols and the corresponding proof rules.

▶ Definition 3 (Protocols). A protocol  $\tau$  comprises a non-empty state set S, a reflexive, transitive transition relation  $\sqsubseteq \subseteq S \times S$ , and two interpretation predicates  $\tau_m(\cdot, \cdot) \in S \times \text{Val} \to \text{Prop}$ with  $m \in \{\text{read}, \text{full}\}$  representing read and full interpretations, respectively. The interpretation predicate has to fulfill the following two laws:

$$\tau_{\rm full}(s,v) \Rightarrow \tau_{\rm full}(s,v) * \tau_{\rm read}(s,v) \qquad \qquad \tau_{\rm read}(s,v) \Rightarrow \tau_{\rm read}(s,v) * \tau_{\rm read}(s,v)$$

We write  $\lfloor \ell : s \mid \tau \rfloor$  (as in GPS) to denote the persistent assertion that  $\ell$  is governed by protocol  $\tau$  and that the protocol has been observed in state s.

The first rule, IGPS-AGREE, represents the guarantee that every protocol is always in a state consistent with all observations, *i.e.*, that all observed states can be linearly ordered w.r.t. to the transition relation  $\sqsubseteq$ .

IGPS-READ enables reading from a location governed by protocol  $\tau$ —allowing the user to observe a future state s' of whatever state s it has previously observed, and providing the associated read interpretation  $\tau_{\text{read}}$ .

Writes to the location are subject to IGPS-WRITE, which allows the user to move the protocol to a "final state" s'—*i.e.*, a state accessible from every state in the protocol—so long as they can provide  $\tau_{\text{full}}$  for s'. This rule may seem very weak, since it forces the protocol into a final state, but this weakness derives from the need to handle the general case where there can be write-write races. Write-write races allow only very limited reasoning: both writes have to prove that their protocol state is later in protocol order to the other one. The write rule presented here solves this problem in a very simple way (see Section 6 for a comparison with the original GPS rule). In Section 4.2, we present a much stronger write rule that is optimized for the common case where there are no write-write races on the location.

Finally, IGPS-CAS governs updates. Its two premises represent the success and failure case, respectively. If the operation succeeds, the value read,  $v_o$ , is guaranteed to belong to a future state s'. The user picks the new state s'' depending on s' and establishes  $\tau_{\text{full}}(s'', v_n)$ , making use of  $\tau_{\text{full}}(s', v_o)$ . In case of a failure, the rule degenerates to IGPS-READ.

## Escrows

A limitation of GPS protocols is that they offer no way to transfer ownership of (nonduplicable) resources from one thread to another unless the receiving thread performs physical synchronization via an update operation. For example, in our MP example, there is no update operation, and yet we want to transfer ownership of the non-atomic location x from the first thread to the second. For such an example, an additional mechanism for ownership transfer is required.

This motivates *escrows*, a mechanism for *logical* synchronization which, unlike protocols, is not tied to physical locations.

▶ **Definition 4 (Escrows).** An escrow  $[P \rightsquigarrow Q]$  consists of a guard resource P and a payload resource Q to be transferred. The guard resource P must be exclusive, i.e.  $P * P \Rightarrow \bot$ . The escrow assertion itself is persistent knowledge (freely duplicable).

The idea of escrows is really just a slight generalization of the "Indiana Jones invariant"  $Inv_x$  that we used in the proof of the MP example from Section 3.1.2. Following the explanation there, the payload resource Q is the "golden idol", the guard resource P is the "bag of sand", and the escrow allows one to swap P for Q. The restriction on exclusivity of P ensures that this swap can only be performed once.

The proof rules for escrows follow the above intuition. IGPS-ESCROW-INTRO places the payload resource Q in escrow. Any thread that learns of the existence of this escrow can then use IGPS-ESCROW-ELIM to trade ownership of the guard resource P for Q.<sup>7</sup>

#### Message passing in iGPS

The verification of MP using iGPS is given in Figure 12. Although the verification is sound for  $\lambda_{\rm RN}$ , it is much simpler than the proof we carried out in the base logic of Iris, and is in fact very close in structure to the SC verification of MP in  $\lambda_{\rm SC}$ . In particular, the Indiana Jones invariant  $\text{Inv}_x$  has now become an escrow **XE**, and the invariant  $\text{Inv}_y$  has now become a (2-state) iGPS protocol **YP**, but otherwise the steps are almost the same. The abstraction of iGPS has relieved us from the burden of reasoning with history and view updates explicitly.

## 4.2 Single-Writer Protocols

As we observed above, the iGPS protocol write rule suffers from a restriction: the user has to transition to a final state. This restriction is not present in CSLs for SC, which let the user pick the future state depending on the current one, much as iGPS-CAS does. Fortunately, in the common case when there are no write-write races to the location, this restriction can be lifted by *single-writer protocols*, a novel invention of iGPS.

A single-writer protocol splits the protocol assertion into two parts: an exclusive writer assertion  $\boxed{\ell:s|\tau}_W$  and a persistent reader assertion  $\boxed{\ell:s|\tau}_R$ . Owning the writer assertion