# On How to Identify Cache Coherence: Case of the NXP QorlQ T4240

Nathanaël Sensfelder

ONERA, Toulouse, France

Julien Brunel

ONERA, Toulouse, France

Claire Pagetti

ONERA, Toulouse, France

#### Abstract

Architectures used in safety critical systems have to pass certain certification standards, which require sufficient proof that they will behave as expected. Multi-core processors make this challenging by featuring complex interactions between the tasks they run. A lot of these interactions are made without explicit instructions from the program designers. Furthermore, they can have strong negative impacts on performance (and potentially affect correctness). One important such source of interactions is cache coherence, which speeds up operations in most cases, but can also lead to unexpected variations in execution time if not fully understood. Architecture documentations often lack details on the implementation of cache coherence. We thus propose a strategy to ascertain that the platform does indeed implement the cache coherence protocol its user believes it to. We also apply this strategy to the NXP QorIQ T4240, resulting in the identification of a protocol (MESIF) other than the one this architecture's documentation led us to believe it was using (MESI).

2012 ACM Subject Classification Computer systems organization  $\rightarrow$  Multicore architectures; Computer systems organization  $\rightarrow$  Real-time systems

Keywords and phrases Real-time systems, multi-core processor, cache coherence

Digital Object Identifier 10.4230/LIPIcs.ECRTS.2020.13

# 1 Introduction

The ever increasing complexity of aircraft and the market's depreciation of single-core processors are motivating the introduction of multi-core processors in aeronautical systems. While the performance gains offered by a switch to these more recent architectures are enticing, this process is impeded by their seemingly unpredictable nature [34], which is inherently incompatible with safety critical environments and aeronautical certification [9]. Still, a number of works are focusing on determining the means required for aircraft manufacturers to fulfill certification expectations despite the complex internal behaviors of multi-core processors COTS (Commercial Off-The Shelves) [1,5,12,26,28].

### 1.1 Cache Coherence – Case of the NXP T4240

Part of this unpredictability can be imputed to the mechanisms that let caches coordinate with one another in order to maintain data coherence without explicit program instructions. There are multiple competing strategies that can be employed to achieve *cache coherence*, and, while the general ideas behind them are known, the details of their implementation tend to be absent from architecture documentations, leaving programmers with the task of finding possibly problematic corner cases and unexpected behaviors.

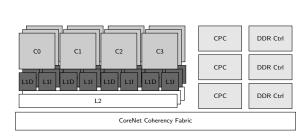

In this paper, we focus on the NXP QorIQ T4240 [14], a PowerPC architecture featuring twelve e6500 cores, each of which is capable of running two simultaneous threads. The cores are equally distributed among three clusters, with one 2MB L2 cache per cluster. These

three L2 caches coordinate and access memory through a complex interconnect called the CoreNet Coherency Fabric. According to their processor's documentation, [13], these clusters implement the MESI cache coherence protocol. More details can be seen in Figure 1, which displays all the cores, caches, and memory controllers present on that architecture.

To be allowed to embed this architecture in an aeronautical system, the designer must be in control of any *transaction* occurring on the platform, that is, any low level behaviors caused by either explicit requests made by a program or by implicit mechanisms of the platform. This also holds true for cache coherence: it is up to the designer to quantify and control the effects on the application software of any transaction generated by this mechanism.

## 1.2 Formal Specification and its Validation

Having to keep implicit mechanisms under control is not an easy task for designers. This is especially true in the case of cache coherence, whose impact is difficult to evaluate even when its rules are made known to the designer.

In this paper, we present our analysis of the NXP QorIQ T4240 cache coherence transactions. This first required us to determine the protocol implemented in the architecture. According to its documentation, the protocol is supposed to be MESI [29] (Modified, Exclusive, Shared, Invalid). To guarantee the proper coverage of all that is involved, we argue for a formal definition of the cache coherence protocol to be made by the designer, based on their current understanding. Such formal definitions do not leave room for any ambiguities. Thus, we have looked for preexisting models of MESI protocol for split-based transaction buses. As it happens, we found none, making our first contribution (Section 3) a formal definition for a split-transaction bus MESI cache coherence protocol, which also corresponds to what we believed the NXP QorIQ T4240 to be using.

This formal MESI protocol definition describes all the transactions it is supposed to be performing. Thus, through the application of our proposed strategy (Section 4) we are able to make use of appropriate stress testing to observe the platform's behavior and compare with what we expected, in effect validating that the architecture does indeed implement the protocol we believe it to. While we developed this strategy around the T4240 and its limited means of observation, we tried to keep our strategy generic enough that it could be soundly used for other targets.

When we applied the strategy to validate the NXP QorIQ T4240, it became apparent the protocol was not actually MESI. Indeed, thanks to the validation strategy, we observed that there were five stable states instead of four and that one of them behaves in a way that led us to recognize a MESIF protocol [17]. We thus had to formally define a split-transaction bus MESIF protocol (Section 6), as we could not find any preexisting definition for it either. We then applied the validation strategy with this new protocol as the starting point, and this time we only found slight implementation choice differences between the supposed and the observed behaviors (Section 7).

In the sequel, we start with a reminder of hardware components and their contribution to the cache coherence. We then detail the contributions described above. We compare our approach with the related works before concluding the paper.

## 2 Cache Coherence

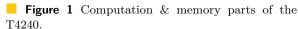

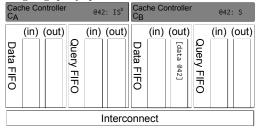

This section provides a reminder of the terminology and of the components involved in the description. Figure 2 provides a visual summary of how all these components interact.

**Figure 2** Components involved in coherence.

## 2.1 The Programs

To keep things simple, we only consider the memory related instructions of programs. Thus, programs are reduced to sequences of load, store, and evict instructions, each being applied to a single given address. Programs do not take into consideration the possibility of either instruction jumping or branching. Addresses are tantamount to memory elements (aligned blocks of memory with the size of a cache line), preventing any possible aliasing. Thus, all considered components, including programs, operate on the same memory unit.

#### 2.2 The Caches

Cache controllers keep copies of memory elements to perform core requests. These copies are acquired through queries on the interconnect. Read-only copies are queried using GetS, read-and-write copies through GetM, and the eviction of a copy can be indicated through PutM. A cache controller may reply to the query of another, providing them with data. They are also able to send data to the coherence manager. Each copy of a memory element held in a cache is attributed a state and, optionally, the identifier of a cache controller.

#### 2.3 The Interconnect

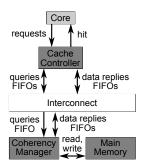

The *interconnect* merely arbitrates the order in which queries are broadcasted. Cache controllers do not directly access the interconnect. Instead, interactions between the cache controllers and the interconnect are all done through FIFO queues. There are four in total for each cache controller: incoming and outgoing queries; and incoming and outgoing data messages. The interconnect follows its access policy when choosing which cache controller's outgoing query queue to poll from next, then enqueues that query to every cache controller's incoming query queue (including that of the one from which the query was taken). Thus, all cache controllers and the coherence manager receive all queries and do so in the same order.

We consider interconnects that support split-transactions, meaning that queries and their replies do not block each other, allowing new queries to be sent before the previous ones receive their replies.

## 2.4 Coherence Manager and Main Memory

Cache controllers do not directly send messages to the system's main memory. Instead, messages meant for the main memory are directed to the *coherence manager*. The coherence manager sees all passing queries. It keeps track of which memory elements are being held by the cache controllers, and has a general idea of their current permissions. In particular, the

coherence manager may consider a cache controller to be the *owner* of a memory element, meaning that this cache controller is tasked with the propagation of the memory element's current value. This lets the coherence manager determine when a query warrants a reply from the main memory.

## 2.5 Terminology

The term request covers all types of communications between a core and its cache controller:  $requests = \{ \texttt{load}, \texttt{store}, \texttt{evict} \}$ . The term message covers both the demands made by cache controllers, and the replies that fullfill them. In other words, messages are all communications that pass through the interconnect:  $messages = queries \cup data \ replies$ , where  $queries = \{\texttt{GetM}, \texttt{GetS}, \texttt{PutM}\}$ , and  $data \ replies = \{\texttt{data}, \texttt{data-e}, \texttt{no-data}\}$ . Note that the actual elements found in queries and  $data \ replies$  depend on the specified protocol. The values given here being for the procotol described in the very next section.

## 3 Formal Description of the MESI Protocol

Our first contribution is the formal definition of a split-transaction MESI protocol that relies on a coherence manager. While the general idea behind MESI is available in many existing works, we did not find any that lists all the possible transient states that can be found in a real implementation (i.e. states other than Modified, Exclusive, Shared, and Invalid). These omissions tend to make the protocol much simpler to understand, but they leave ambiguities in the behavior of the protocol. Our description is a conjecture based on [31], which presents a complete definition of the MESI protocol, but that is limited to architectures featuring an atomic bus. Atomic buses only allow a single transaction (query and reply) to occur at any given time, which greatly narrows the number of transient states the system can find itself in.

#### 3.1 Protocol Specification

MESI is based on the MSI protocol, so named because it features three stable states: *Modified*, which indicates read-and-write permissions of a memory element; *Shared*, for read-only permissions; and *Invalid*, the default one, indicating an absence of permissions. Introduced in [29], the MESI protocol adds a fourth stable state, *Exclusive*, which indicates that not only does the cache controller have read-only permissions, but also that no other cache currently holds any permission to access the memory element. This allows the cache controller to upgrade to read-and-write permissions without having to perform a costly communication. Just as it is used to keep track of whether a cache holds a read-and-write copy of a memory element in the MSI protocol, this definition of the MESI protocol uses the coherence manager to detect when a cache can be said to be the sole owner of a memory element.

This version of the MESI protocol uses three types of data replies: data, data-e, and no-data. data indicates that the value associated with the memory element is sent. By sending a no-data reply, cache controllers can indicate to the coherence manager that the memory element has been discarded (its value is not part of the reply). The coherence manager can send data-e replies, which are equivalent to data, with the added information that the recipient is its sole owner.

Our description of the MESI protocol can be seen in Table 1. It is split in two tables, one defining the cache controllers' behavior, the other the coherence manager's. In effect, these tables indicate a sequence of actions to be performed when faced with an incoming event (be it a request or a message).

**Table 1** Description of the MESI protocol.

|                          | Cache Controller |              |            |                        |                                                                                                   |                                                                                                                          |                                       |                        |      |

|--------------------------|------------------|--------------|------------|------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------|------|

| State                    | (                | Core Request | t          | Interconnect<br>Access | Data                                                                                              | Reply                                                                                                                    | Rece                                  | ived Queries           |      |

|                          | load             | store        | evict      |                        | data                                                                                              | data-e                                                                                                                   | GetS                                  | GetM                   | PutM |

| I                        | GetS?, ISBD      | GetM?, IMBD  | hit        |                        |                                                                                                   |                                                                                                                          | -                                     | -                      | -    |

| IS <sup>BD</sup>         | stall            | stall        | stall      | IEoS <sup>D</sup>      | ISB                                                                                               | IE <sup>B</sup>                                                                                                          | -                                     | -                      | -    |

| $IS^B$                   | stall            | stall        | stall      | S                      |                                                                                                   |                                                                                                                          | -                                     | -                      |      |

| ISD                      | stall            | stall        | stall      |                        | r← ∅,<br>S                                                                                        | $r!data$ , $m!no-data$ , $r \leftarrow \emptyset$ , $S$                                                                  | -                                     | ISDI                   |      |

| $IEoS^D$                 | stall            | stall        | stall      |                        | S                                                                                                 | E                                                                                                                        | r←s, IS <sup>D</sup>                  | r←s, IS <sup>D</sup> I |      |

| IS <sup>D</sup> I        | stall            | stall        | stall      |                        | $\begin{array}{c} \text{load hit,} \\ \mathbf{r} \leftarrow \emptyset, \\ \mathbf{I} \end{array}$ | $\begin{array}{c} \text{load hit,} \\ \text{r} \leftarrow \emptyset, \\ \text{r!data,} \\ \text{m!no-data,} \end{array}$ | -                                     | -                      |      |

| $IM^{BD}$                | stall            | stall        | stall      | IMD                    | IMB                                                                                               |                                                                                                                          | -                                     | -                      | -    |

| $IM^B$                   | stall            | stall        | stall      | М                      |                                                                                                   |                                                                                                                          | -                                     | -                      | -    |

| $IM^D$                   | stall            | stall        | stall      |                        | М                                                                                                 |                                                                                                                          | r←s, IM <sup>D</sup> S                | r←s, IM <sup>D</sup> I |      |

| IM <sup>D</sup> I        | stall            | stall        | stall      |                        | store hit,<br>r!data,<br>r← ∅, I                                                                  |                                                                                                                          | -                                     | -                      |      |

| IM <sup>D</sup> S        | stall            | stall        | stall      |                        | store hit,<br>r!data,<br>m!data,<br>$r \leftarrow \emptyset$ , S                                  |                                                                                                                          | -                                     | IM <sup>D</sup> SI     |      |

| IMDSI                    | stall            | stall        | stall      |                        | store hit,<br>r!data,<br>m!data,<br>$r \leftarrow \emptyset$ , I                                  |                                                                                                                          | -                                     | -                      |      |

| S                        | hit              | GetM?, SMBD  | hit, I     |                        |                                                                                                   |                                                                                                                          | _                                     | I                      |      |

| SM <sup>BD</sup>         | hit              | stall        | stall      | SM <sup>D</sup>        | SM <sup>B</sup>                                                                                   |                                                                                                                          | _                                     | IM <sup>BD</sup>       |      |

| SM <sup>B</sup>          | hit              | stall        | stall      | M                      | Dir.                                                                                              |                                                                                                                          | -                                     | IM <sup>B</sup>        |      |

| SM <sup>D</sup>          | hit              | stall        | stall      | T1                     | store hit, M                                                                                      |                                                                                                                          | r←s, SM <sup>D</sup> S                | r←s, SM <sup>D</sup> I |      |

| SM <sup>D</sup> I        | hit              | stall        | stall      |                        | store hit, r!data, $r \leftarrow \emptyset$ , I                                                   |                                                                                                                          |                                       | -                      |      |

| $SM^DS$                  | hit              | stall        | stall      |                        | store hit,<br>r!data,<br>m!data,<br>$r \leftarrow \emptyset$ , S                                  |                                                                                                                          | -                                     | SM <sup>D</sup> SI     |      |

| SM <sup>D</sup> SI       | hit              | stall        | stall      |                        | store hit, $r!data$ , $m!data$ , $r \leftarrow \emptyset$ , I                                     |                                                                                                                          | -                                     | -                      |      |

| М                        | hit              | hit          | PutM?, MIB |                        |                                                                                                   |                                                                                                                          | m!data,<br>s!data, S                  | s!data, I              |      |

| $\mathtt{MI}^\mathtt{B}$ | hit              | hit          | stall      | m!data, I              |                                                                                                   |                                                                                                                          | m!data,<br>s!data, II <sup>B</sup>    | s!data, IIB            |      |

| $II^B$                   | stall            | stall        | stall      | I                      |                                                                                                   |                                                                                                                          | -                                     | -                      | -    |

| Е                        | hit              | hit, M       | PutM?, EIB |                        |                                                                                                   |                                                                                                                          | m!no-data,<br>s!data, S               | s!data, I              |      |

| IEB                      | stall            | stall        | stall      | E                      |                                                                                                   |                                                                                                                          | -                                     | -                      | -    |

| EIB                      | hit              | stall        | stall      | m!no-data, I           |                                                                                                   |                                                                                                                          | m!no-data,<br>s!data, II <sup>B</sup> | s!data, IIB            |      |

|       | Coherence Manager                |                |                               |                 |                          |           |  |  |

|-------|----------------------------------|----------------|-------------------------------|-----------------|--------------------------|-----------|--|--|

| State | Re                               | ceived Queries |                               |                 | Data Reply               |           |  |  |

| State | GetS                             | GetM           | PutM<br>(Owner)               | PutM<br>(Other) | data                     | no-data   |  |  |

| I     | read, s!data-e, r←s, M           | s!data, r←s, M |                               | -               |                          |           |  |  |

| М     | $r \leftarrow \emptyset$ , $S^D$ | r←s            | $r \leftarrow \emptyset, I^D$ | -               | write, IoS <sup>B</sup>  | IoSB      |  |  |

| $I_D$ | stall                            | stall          | stall                         | -               | write, resume, I         | resume, I |  |  |

| $S^D$ | stall                            | stall          | stall                         | -               | write, <b>resume</b> , S | resume, S |  |  |

| IoSB  | r← ∅, S                          | r←s, M         | r← ∅, I                       | -               |                          |           |  |  |

| S     | read, s!data                     | s!data, r←s, M |                               | -               |                          |           |  |  |

In the cache controller's table, columns correspond to the following: *state* refers to the state attributed to the local copy of the memory element by the cache controller. The three *Core request* columns indicate the actions that are performed when receiving a request from the core. *Interconnect access* specifies actions for when the cache controller reads one of its own queries. The *data reply* columns are for when the cache controller receives one of the types of data replies. Lastly, the *received queries* columns are for the reception of queries originating from other cache controllers. The table defining the coherence manager follows the same principles, but does not have columns for core requests, as it cannot receive them, nor for access to the interconnect, as it does not emit queries.

Let us now expand on the semantics of the actions found in these tables. Cache controllers may send queries on the bus (e.g. sending a GetS query is noted as GetS?). They can also change the state they attribute to a memory element (e.g. moving to the I state, which is noted I). If a request coming from their core can be fulfilled without further actions, the table indicates it with hit. A similar notation is used to indicate that the oldest request of a given type has just been completed (e.g. load hit). As a reaction to an incoming query, cache controllers can mark their copies of memory elements as being associated with the cache controller that sent the query (noted  $r \leftarrow s$ ). This can later be used to send a data message to that cache controller (e.g. r!data). Data can also be sent as a reply to an incoming query (e.g. s!data), or to the coherence manager (e.g. m!no-data). The stall action marks that the cache controller is unable to handle the incoming request at the moment. This request is put into a waiting queue until the memory element changes state, at which point it is re-evaluated.

The coherence manager follows a similar syntax, with the exception of the stall action, which now blocks *any* incoming query until the next resume action (data messages are not blocked, however). The other additions are the write and read actions, which respectively indicate that the memory controller either writes the received value or reads the current one.

### 3.2 Examples of Behaviors

Here are some examples of remarkable behaviors exhibited by this definition of the MESI protocol.

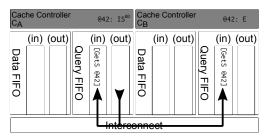

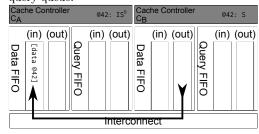

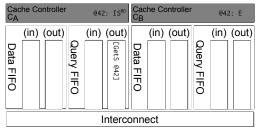

- ▶ Example 1 (Reaching S). This example is meant to showcase how exchanges between cache controllers are assumed to take place. To keep things simple, we only consider two cores and a single memory element (whose address is 42). This example is illustrated as a sequence in Figure 3.

- ▶ Example 2 (Reaching E). To hold a memory element in the E state, a cache must be the only one to have a copy of that memory element. The caches rely on the coherence manager to know when it is the case. The coherence manager uses its I state to mark memory elements that are sure to not be in any caches. Thus, if no cache controllers hold the memory element and the coherence manager is in I, whenever a core loads the data it becomes E in its cache. The behavior is similar to Figure 3 except that the main memory will provide the data.

It is important to notice that it is not easy for the coherence manager to detect whether a cache controller is the sole owner. Indeed, the coherence manager is not always able to know that all caches have evicted their copy of a memory element: in Table 1, the cache controller's table indicates that an eviction from S does not lead to any message. The only way for the coherence manager to return to the I state is for a cache to evict its copy of a memory element in either the E or M state without another cache asking for a copy.

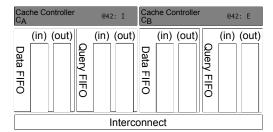

(a) In the initial phase, one cache controller,  $C_A$ , holds that memory element in the I state, while the other,  $C_B$ , holds it in the E state.

(c) The interconnect broadcasts outgoing queries from caches to all the incoming query queues. As  $C_A$  is the only one with an outgoing query, the GetS is added to both its own and  $C_B$ 's incoming query queue.

(e) Data messages are not broadcasted, but instead only added to the incoming data queue of a targeted cache controller (or the coherence manager's). Thus, the reply is moved from  $C_B$ 's outgoing reply queue to  $C_A$ 's incoming one.

(b) Next, we consider that  $C_A$ 's core issued a load instruction on 42. This leads  $C_A$  to move to the  $\mathbf{IS}^{\mathtt{BD}}$  state, and to issue a **GetS** query to its outgoing query queue.

(d) Consuming the message in their incoming query queues, both  $C_A$  and  $C_B$  change state, moving to  $\mathtt{IS}^{\mathtt{D}}$  and  $\mathtt{S}$  respectively. In addition,  $C_B$  adds its reply for the query to its outgoing data queue.

(f) Finally,  $C_A$  consumes the message in its incoming data queue, changing its state to S and fulfilling its core's request.

▶ Example 3 (Sharing from E). From the coherence manager's point of view, there is no difference between a cache controller owning a memory element in the E state and one in the M state. Thus, if there is a cache owning a copy of a memory element in the E state, the coherence manager will assume that this cache may have modified the value and that the main memory no longer holds the correct value. As a result, the cache holding the Exclusive copy of the memory element will transfer it to any other cache that asks for it. If this is caused by another cache demanding a read-only copy (GetS), the coherence manager will expect an update on the value of the memory element. This update can come in two forms: either the cache that exclusively held the memory element made a modification (in which case it would have moved to the Modified state) and sends a data message, or it has not and it sends a no-data message.

#### 3.3 System Behavior

The cache coherence protocol is defined for a single address and a single cache controller. However, what we are interested in is a multi-core architecture executing a program. Thus, we need to model the behavior of the overall platform to identify and quantify the transactions generated by the cache coherence. To do so, we use an automaton where each state corresponds to the system state and transitions between states are events produced by one or several components (core, cache controller, interconnect, coherence manager or memory). In this section we formally define such automata.

- ▶ **Definition 4** (Memory Element State). Let  $S_s$  (resp.  $T_s$ ) denote the set of stable (resp. transient) states. From the point of view of a cache controller or a coherence manager, a memory element m can be in any valid stable or transient states, i.e.,  $m \in S_s \cup T_s$ . We denote by  $G_s$  the set of states  $G_s = S_s \cup T_s$  of a cache controller and  $G_{CM}$  those of the coherence manager.

- ▶ Example 5. In the MESI protocol defined in Table 1, the states of the cache controllers are  $S_s = \{M, E, S, I\}$  and  $\mathcal{T}_s = \{IS^{\mathrm{BD}}, IS^{\mathrm{D}}, \ldots\}$ . The states of the coherence manager are  $S_s = \{M, S, I\}$  and  $\mathcal{T}_s = \{I^{\mathrm{D}}, S^{\mathrm{D}}, IoS^{\mathrm{B}}\}$ .

- ▶ **Definition 6** (Cache Controller State). Let Addr denote the set of all memory element addresses. We define the state of a cache controller CC (resp. of a coherence manager CM) as the function  $s_{CC}$ : Addr  $\rightarrow \mathcal{G}_s$  (resp.  $s_{CM}$ : Addr  $\rightarrow \mathcal{G}_{CM}$ ).

- ▶ Definition 7 (System State). Let us consider an architecture  $\langle CC_1, \ldots, CC_n, CM \rangle$  composed of n cache controllers  $CC_i$  and a coherence manager CM. The global state of the architecture consists of the states of all memory elements in all cache controllers and in the coherence manager. Let Addr be the set of all memory element addresses, the global state  $s: Addr \to \mathcal{G}_s^n \times \mathcal{G}_{CM}$  is defined as  $\forall m \in Addr, s(m) = \langle s_{CC_1}(m), \ldots, s_{CC_n}(m), s_{CM}(m) \rangle$  where  $s_{CC_i}$  is the state of the cache controller  $CC_i$  as defined in Definition 6. For the sake of simplicity and without loss of the generality, in the sequel, we will only focus on a given address m and define the state of a cache controller as an element in  $\mathcal{G}_s$  and of the system as a tuple in  $\mathcal{G}_s^n \times \mathcal{G}_{CM}$ .

- ▶ **Definition 8** (Valid State). Not all combinations of states are valid, e.g. two cache controllers cannot be in M for the same address at the same time. We note  $\mathcal{V} \subseteq \mathcal{G}_s^n \times \mathcal{G}_{CM}$  the set of valid system states.

- ▶ **Definition 9** (Event). We distinguish between explicit (or controllable) events  $E_E = requests = \{load, store, evict\}$ , which are made by the user, and the implicit (or uncontrollable) events  $E_I = messages \cup \{bus\}$  (where bus corresponds to the cache seeing one of its own query being broadcasted on the interconnect), which are made by the architecture. Thus, on a given cache controller, the possible events are  $E_E \cup E_I \cup \{-\}$  where represents the special event where nothing happens.

The set of events over the system is denoted by  $E \subseteq (E_E \cup E_I \cup \{-\})^n$  (not all combinations of events are possible).

The system event  $\langle -, \ldots, -, e, -, \ldots, - \rangle$  consisting of one event e in the cache controller of id i, and nothing in all the other cache controllers, is simply denoted by  $\langle e, i \rangle$ .

▶ **Definition 10** (Automaton of the system). The behavior of the system is defined by the automaton  $\langle \mathcal{V}, E, s_{init}, Tr \rangle$  where  $s_{init} = \langle I, \dots, I \rangle$  is the initial state and  $Tr : \mathcal{V} \times E \to \mathcal{V}$  is the transition function.

- **▶ Example 11.** Using the MESI protocol and 2 cache controllers, we have for instance  $\text{Tr}(\langle I,I,I\rangle,\langle load,-\rangle)=\langle IS^{\text{BD}},I,I\rangle$ . As the event is a single component event, we could also use the notation mentioned above  $\langle load,1\rangle=\langle load,-\rangle$  meaning that the cache controller with id 1 does a load, whereas all the other do nothing. If we detail all the implicit events leading to the next stable states, we have:  $\text{Tr}(\langle IS^{\text{BD}},I,I\rangle,\langle \text{bus},GetS,GetS\rangle)=\langle IEoS^{\text{D}},I,M\rangle$  (the interconnect broadcasts the GetS);  $\text{Tr}(\langle IEoS^{\text{D}},I,M\rangle,\langle \text{data-e},1\rangle)=\langle E,I,M\rangle$  (the cache coherence triggers the memory which provides the requested data).

- ▶ Example 12 (Simultaneous requests). Still using the MESI protocol and 2 cache controllers, there may be several simultaneous requests, e.g.  $\langle load, store \rangle$ . In such situations, because of the internal dynamics of the interconnect and memory (Round Robin access, delays . . .) all combinations of interleaving are envisaged. For instance  $\text{Tr}(\langle I, I, I \rangle, \langle load, store \rangle) = \langle IS^{\text{BD}}, IM^{\text{BD}}, I \rangle$  (all local requests are handled). Then, among the possible next steps are both  $\text{Tr}(\langle IS^{\text{BD}}, IM^{\text{BD}}, I \rangle, \langle bus, GetS \rangle) = \langle IEoS^{\text{D}}, IM^{\text{BD}}, M \rangle$  (the interconnect chooses the first core first) or  $\text{Tr}(\langle IS^{\text{BD}}, IM^{\text{BD}}, I \rangle, \langle GetM, bus \rangle) = \langle IS^{\text{BD}}, IM^{\text{D}}, M \rangle$  (the interconnect chooses the second core first). Thus, several paths leave from  $\text{Tr}(\langle I, I, I \rangle, \langle load, store \rangle)$  and they may ultimately lead to separate stable states:  $\langle I, M, M \rangle$  if the data reply has reaches core 1 first, or  $\langle S, S, S \rangle$  if the data reply reaches core 2 first.

- ▶ **Definition 13** (Path). A path in a system automaton corresponds to a succession of transitions, from one state to another, that has been triggered by a controllable event and is followed by a series of adequate implicit events. A path from s to s' triggered by e is denoted by  $p: s \leadsto^e s'$ .

- ▶ **Example 14.** The successive transitions that have been described in Example 11 define the path  $\langle I, I, I \rangle \leadsto^{\langle load, 1 \rangle} \langle E, I, M \rangle$ .

- ▶ **Definition 15.** From the transition function Tr, we define the observable transition function  $Tr_i^{\star}$ , in the case of single controllable events, as follows:  $\forall c \in \mathcal{V}, e \in E_E$   $Tr_i^{\star}(c, \langle e, i \rangle) = c'$  such that  $c \leadsto^{\langle e, i \rangle} c'$  and no implicit event may be induced by  $\langle e, i \rangle$  upon reaching c'.

For simultaneous explicit events, the observable transition function is defined by composing the observable transition function for each explicit event, taken as a single event. Notice that it is an expected property of the protocol, which we do not study here, that all possible orderings provide the same system state.

- ▶ **Example 16.** Considering a single event:  $\operatorname{Tr}_i^{\star}(\langle I, I, I \rangle, \langle load, 1 \rangle) = \langle E, I, M \rangle$ . Let us now consider multiple events:  $\operatorname{Tr}_i^{\star}(\langle I, I, I \rangle, \langle load, store \rangle) = \{\langle S, S, S \rangle, \langle I, M, M \rangle\}$ .

- ▶ **Definition 17** (Number of Events). We define the function NbEvent:  $\mathcal{P}ath \times 1...n \to \mathbb{N}^3$  (with n the number of cores in the architecture) which associates to each path and core id, the number of accesses to the bus, the number of received queries, and the number of received data replies for the cache controller identified by this id.

- ▶ Example 18. Let us consider the path  $p:\langle I,I,I\rangle \leadsto^{\langle load,1\rangle} \langle E,I,M\rangle$ . Then  $NbEvents(p,1) = \langle 1,1,1\rangle$  because core 1 has accessed to the bus once, received its own GetS and the data reply to its request.  $NbEvents(p,2) = \langle 0,1,0\rangle$  because core 2 has simply received the GetS generated by core 1.

# 4 Validation Strategy

This section presents our proposed strategy to assert that a given architecture does indeed implement a given previously defined cache coherence protocol. We have fully defined the

system behavior in Section 3.3 and ideally we would recognize all the automata on the architecture. Unfortunately, we cannot simply observe the states and events as we previously defined them. Instead, we observe flags and performance counters, to which we need to link the notion of states and events. Even worse, our observations are only partial, with some information missing. Thus, in addition to linking the observations to the automaton, we also have to infer the missing elements. We illustrate our ideas on the NXP QorIQ T4240 platform, however, the reasoning could be leveraged for other types of architecture.

#### **Observable States**

- ▶ Property 1 (T4240 Observable Flags). We can observe flags with Code Warrior, the official debugging suite for this architecture. While a lot of information is available, we consider the relevant cache line flags to be: Dirty, Valid, Share, Exclusive and LastReader. Those flags take Boolean value and only provide information on stable states. Indeed, no combination of flags correspond to any transient state. Instead, their value changes upon entering the next stable state following the execution of a request (load, store, or evict) or because of an external query.

- ▶ Definition 19 (Observable Cache Controller State). Let us consider an architecture with p Boolean flags, an observable state o for a cache controller is a combination of values of the flags  $o = \langle f_1, \ldots, f_p \rangle$ . Let  $\mathcal{R}$  denote the set of cache controller states that can be really observed on a given architecture.

- ▶ Issue 1 (Matching Observable Cache Controller States and Stable States). For validating that an architecture indeed implements a cache protocol, we need to associate each observed state with a protocol state. More precisely, we need to identify a function  $\operatorname{Decode}: \mathcal{R} \to \mathcal{G}_s$  such that  $\operatorname{Decode}$  is surjective:  $\forall f \in \mathcal{G}_s$ ,  $\exists r \in \mathcal{R}$ ,  $\operatorname{Decode}(r) = f$ .

Indeed, while having multiple observed states corresponding to the same state is perfectly acceptable at this point (the different states may end up being identical from the cache coherence's point of view), the reverse is not true: if an observed cache coherence state is attributed to multiple formally defined state, the analysis considers that the protocols do not match. This can be caused by missing information (unable to observe the information that would split the observed state into multiple ones). This is the reason why Decode has to be surjective.

▶ Example 20. For the T4240, the observable state  $\langle Dirty = \text{false}, Valid = \text{false}, Share = \text{false}, Exclusive = \text{false}, LastReader = \text{false} \rangle$  is the initial observable state and corresponds to the I stable state.

The tools at our disposition do not expose anything related to the coherence manager.

- ▶ **Property 2** (No Observation Available from the Coherence Manager). We do not have any possibility of observing the coherence manager directly.

- ▶ Definition 21 (Observable System State). Let us consider an architecture  $\langle CC_1, \dots, CC_n, CM \rangle$  composed of n cache controllers  $CC_i$  and a coherence manager CM. The observable system states are the observable states of each  $CC_i$  and the CM.

- ▶ **Example 22.** On the T4240, the observable system states are the observable states of each cache controller only. Thus, to match the observable state and the real state we have to infer the non observable elements.

▶ Issue 2 (Matching Observable States and System States). To validate that an architecture indeed implements a given cache protocol, we need to identify a function  $\operatorname{Decode}: \mathcal{R}^n \to \mathcal{V}$  associating a tuple of observable states with a system state, which is directly defined from the function  $\operatorname{Decode}$  of Issue 1 and that is also surjective:  $\forall f \in \mathcal{V}, \exists r \in \mathcal{R}^n, \operatorname{Decode}(r) = f$ .

## Controllable Events and Reachable Observable States

- ▶ Property 3 (T4240 controllable events). On each core, we can execute programs. Thus, to induce implicit cache coherence traffic, we can only trigger some request (load, store or evict) and observe the reached observable states. We have defined a series of benchmarks that can either run a single request on a core or multiple requests on several cores.  $\operatorname{Reach}(C, \langle \operatorname{instr}, k \rangle)$  denotes the observable state after executing the single request instr on the core k from the observable state C. In addition,  $\operatorname{Reach}_m(C, \langle \operatorname{instr}_1, \ldots, \operatorname{instr}_n \rangle)$  denotes the observable states after executing the simultaneous requests  $\operatorname{instr}_i \in \{\operatorname{load}, \operatorname{store}, \operatorname{evict}, -\}$  on each core from the observable state C.

- ▶ **Definition 23** (Reachable System States). From an architecture in an initial state in which no memory elements are stored in the caches, we can explore the reachable system states by executing benchmarks that trigger requests.

- ▶ Definition 24 (Step 1: Reachability Analysis). Starting from the initial situation where all cache controllers consider the memory element to be invalid, we compute the reachable observable system states by observing the effect of a single core instruction and the associated transition relation Reach. The idea is to run a benchmark and observe the reached state. If this state has not been visited, it is added to  $\mathbb{R}^n$ , otherwise it is not. This is a basic reachability algorithm.

```

\begin{array}{l} \mathcal{R}^n \leftarrow \{ \text{init} \} \\ Candidates \leftarrow \{ \langle \text{init} \rangle \} \\ \textbf{while} \ (Candidates \neq \emptyset): \\ C \in Candidates; \\ Candidates \leftarrow Candidates/C; \\ \textbf{foreach} \ k \leq n \\ \textbf{foreach} \ instr \in \{ load, store, evict \} \\ ObservedState \leftarrow benchmark(C, \ \langle instr \ , \ k \rangle) \\ \textbf{Reach} \ (C, \ \langle instr \ , \ k \rangle) \leftarrow ObservedState \\ \textbf{if} \ ObservedState \not\in \mathcal{R}^n \\ \mathcal{R}^n \leftarrow \mathcal{R}^n \cup \{ ObservedState \} \\ Candidates \leftarrow Candidates \cup \{ ObservedState \} \\ Events[C, \ ObservedState] \leftarrow PerformanceCounters \\ \end{array}

```

- ▶ Issue 3. To be valid, the matching between observable states and system states must be consistent with the transitions of both protocols. That is, the function Decode has to be a simulation relation:  $\forall o \in \mathcal{R}^n, \ \forall c \leq n, \ \forall i \in \text{requests}, \ \text{Decode}(\text{Reach}(o, \langle i, c \rangle)) = Tr_i^*(\text{Decode}(o), \langle i, c \rangle).$

- ▶ **Example 25.** For the T4240, the observable state  $f_0 = \langle Dirty = \text{false}, Valid = \text{false}, Share = \text{false}, Exclusive = \text{false}, LastReader = \text{false} \rangle$  is the initial observable state and corresponds to the I stable state; whereas  $f_1 = \langle Dirty = \text{false}, Valid = \text{true}, Share = \text{false}, Exclusive = \text{true}, LastReader = \text{false} \rangle$  seems to be E. When running the benchmark  $\langle \text{load}, 1 \rangle$  on core 1 from  $f_0$ , the reached observable state is  $f_1$ , which allows for the possibility of  $f_1$  being E.

#### **Observable Events**

The performance registers can count the number of occurrences of predefined events. While the name and identification code for each performance event is indicated in the architecture's documentation, the meaning behind their name is not always obvious.

- ▶ **Property 4** (T4240 Performance Counters). *Below is a list of the events of interest, as well as their meaning based on our understanding.*

- L2 Data Accesses Accesses made to the L2 cache.

- **L2 Snoop Hits** External queries on a memory element held by this cache.

- L2 Snoop Pushes Replies given to snooped queries.

- **External Snoop Requests** External queries.

- L2 Reloads From CoreNet Replies received.

- L2 Snoops Causing MINT Replies to a snooped query when holding the memory element in a dirty (modified) state.

- L2 Snoops Causing SINT Replies to a snooped query when holding the memory element in a clean (unmodified) state.

- CPU Cycles

- ▶ **Definition 26** (Observable Cache Controller Associated Events). Let us consider an architecture with p Integer counters, an observable event f for a cache controller is a combination of values of the counters  $o = \langle f_1, \ldots, f_p \rangle$ . The set of cache controller associated events that can be really observed on a given architecture is denoted by  $\mathcal{N}$ .

- ▶ **Issue 4.** To be valid, the matching between observable states and system states must be consistent with the events associated with the transitions of both protocols. That is, for single instructions,  $\forall o \in \mathbb{R}^n$ ,  $\forall c \leq n$ ,  $\forall i \in \text{requests}$ ,  $\forall j \in 1...n$ ,

Events  $[o, \operatorname{Reach}(o, \langle i, c \rangle), j] = \operatorname{NbEvents}(\operatorname{Decode}(o) \leadsto^{\langle i, c \rangle} \operatorname{Decode}(\operatorname{Reach}(o, \langle i, c \rangle)), j)$  where Events stores the performance counters, seen from core j, in the benchmark going from o to  $\operatorname{Reach}(o, \langle i, c \rangle)$  (as done in the algorithm of step 1).

For multiple simultaneous instructions:  $\forall o \in \mathcal{R}^n, \ \forall e_1, \dots, e_n \in \text{requests} \cup \{-\}, \ \forall j \in 1...n, \ \forall s \in \textit{Reach}_m(o, \langle e_1, \dots, e_n \rangle), \ \text{Events}[o, s, j] = \text{NbEvents}(\textit{Decode}(o) \leadsto^{\langle e_1, \dots, e_n \rangle})$ Decode(s), j).

- ▶ Example 27. Continuing Example 25, when running the benchmark  $\langle 1 \text{oad}, 1 \rangle$  on core 1 from  $f_0$ , we also collect the observable events and we observe that: on core 1, there are 2 L2  $Data\ Accesses$  (1 for the data-e, all such messages are duplicated as explained in the next section) and 1 L2  $Reloads\ From\ CoreNet$  (1 for the GetS); on core 2, there is 1  $External\ Snoop\ Requests$  (1 for the GetS); which still allows  $f_1$  to be E.

- ▶ **Definition 28** (Step 2: Reachability Analysis with Simultaneous Requests). In addition to step 1 (see Definition 24), for the multiple simultaneous requests, we need to run additional benchmarks. The idea is similar, except that instead of running benchmark(C,  $\langle instr, k \rangle$ ), we apply benchmark(C,  $\langle instr_1, \ldots, instr_n \rangle$ ) for the tuples  $\langle instr_1, \ldots, instr_n \rangle$  in a pre-computed list.

- ▶ Example 29. Consider that we have run the benchmark  $\langle load, store, \rangle$  from the initial state and we believe that this coincides with the path  $\langle I, I, I \rangle \leadsto^{\langle load, store, \rangle} \langle I, M, M \rangle$  then we have to count on the core 1: 1 access to the interconnect, 2 queries and 2 data replies.

# 5 Evaluating Cache Coherence on the T4240

In this section, we illustrate our proposed process by attempting to validate the MESI protocol we defined on the NXP QorIQ T4240 architecture. Much to our surprise, the results quickly conclude that this architecture does not implement MESI.

## 5.1 The NXP QorlQ T4240 Experimental Setup

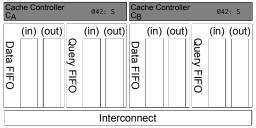

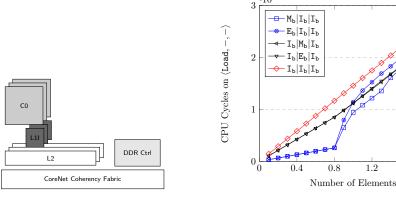

**Figure 4** Configuration of the T4240.

**Figure 5** Exposing Cache Eviction.

1.6

$\cdot 10^4$

In order to limit the mechanisms observed to the L2 cache coherence, we chose to disable the architecture's L1 Data caches. Furthermore, we only consider a single core (and execution thread) per cluster, and thus, per L2 cache. In an attempt at reducing the impact of instruction fetching, we keep the L1 Instruction caches enabled. Lastly, our system only uses a single memory controller. Thus, our configuration resembles the one shown in Figure 4, the remaining hardware configuration being left to what it is by default.

The NXP QorIQ T4240 architecture does not feature the evict instruction. The closest available instruction (dcbi, Data Cache Block Invalidate) results in the element being evicted from all the caches, which is significantly different, unless that element has been marked as ignored by cache coherence (which is then pointless for our purposes). Since our benchmarks are very small programs dealing almost exclusively with the set of experimental memory elements, we replaced the application of an evict on all of the memory elements with a simple invalidation of the whole local cache, which does still involve cache coherence.

While related to caches and an important factor of their performance, the issue of replacement policy is orthogonal to the cache coherence protocol. Thus, we do not want its effects to be mixed in our benchmarks. Through testing (see Figure 5), we concluded that caches started evicting cache lines when holding somewhere between 8000 and 9000 of them. From the information given in [13], we speculate that this corresponds to the 8192 cache lines held in a bank.

## 5.2 Partial Matching of States with Step 1

We listed and named every combination we have encountered in Table 2. We made an initial matching that seems coherent with the flags name, but that still needs to be checked by looking at the transitions. We denote by a  $_{\rm b}$  suffix the states observed on the platform.

We check the property required by Issue 3 that applying any request (load, store, and evict) from a matched state leads to the correct matched state. Table 3 shows the original and destination state for a memory element on each of the three clusters according

#### 13:14 Identifying Cache Coherence on the NXP QorlQ T4240

**Table 2** Stable States of the T4240 L2 Caches Protocol.

| State               | Dirty | Valid    | Share | Exclusive | LastReader |

|---------------------|-------|----------|-------|-----------|------------|

| M <sub>b</sub>      | ✓     | ✓        |       |           |            |

| E <sub>b</sub>      |       | ✓        |       | ✓         |            |

| $I_b$               |       |          |       |           |            |

| $arphi_{	exttt{b}}$ |       | ✓        |       |           | ✓          |

| $\chi_{\mathtt{b}}$ |       | <b>√</b> | ✓     |           |            |

#### **Table 3** State Changes.

|                                                                                     | $\langle { m Load},$                                                                    | -,->                                                 | $\langle \text{Store,-,-} \rangle$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         | $\langle \text{Evict,-,-} \rangle$                                                      |                                                      |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------|

| Onigin                                                                              | Destina                                                                                 | tion                                                 | Destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                         | Destination                                                                             |                                                      |

| Origin                                                                              | Observ                                                                                  | Match                                                | Observ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Match                   | Observ                                                                                  | Match                                                |

| $\langle \mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b} \rangle$ | $\langle \mathtt{E}_\mathtt{b} , \mathtt{I}_\mathtt{b} , \mathtt{I}_\mathtt{b} \rangle$ | $\langle \texttt{E,I,I} \rangle$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |                                                                                         |                                                      |

| $\langle \mathtt{E}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b} \rangle$ | $\langle \mathtt{E}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b} \rangle$     | $\langle \texttt{E,I,I} \rangle$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         | $\langle \mathtt{I}_\mathtt{b} , \mathtt{I}_\mathtt{b} , \mathtt{I}_\mathtt{b} \rangle$ | $\langle \mathtt{I}, \mathtt{I}, \mathtt{I} \rangle$ |

| $\langle \mathtt{M}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b} \rangle$ | $\langle \mathtt{M}_\mathtt{b} , \mathtt{I}_\mathtt{b} , \mathtt{I}_\mathtt{b} \rangle$ | $\langle \texttt{M,I,I} \rangle$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |                                                                                         |                                                      |

| $\langle \mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{M}_\mathtt{b} \rangle$ | $\langle arphi_{	t b}$ , ${	t I}_{	t b}$ , $\chi_{	t b}  angle$                         | $\langle \mathtt{S,I,S} \rangle$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         | $\langle \mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{M}_\mathtt{b} \rangle$     | $\langle \texttt{I,I,M} \rangle$                     |

| $\langle \mathtt{I}_\mathtt{b},\mathtt{I}_\mathtt{b},\mathtt{E}_\mathtt{b} \rangle$ | $\langle arphi_{	t b}$ , ${	t I}_{	t b}$ , $\chi_{	t b}  angle$                         | $\langle \mathtt{S,I,S} \rangle$                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         | $\langle \mathtt{I}_\mathtt{b} , \mathtt{I}_\mathtt{b} , \mathtt{E}_\mathtt{b} \rangle$ | $\langle \texttt{I,I,E} \rangle$                     |