Report from Dagstuhl Seminar 15121

# Mixed Criticality on Multicore/Manycore Platforms

Edited by

Sanjoy K. Baruah<sup>1</sup>, Liliana Cucu-Grosjean<sup>2</sup>, Robert I. Davis<sup>3,2</sup>, and Claire Maiza<sup>4</sup>

- 1 University of North Carolina at Chapel Hill, US, baruah@cs.unc.edu

- 2 INRIA Roquencourt Le Chesnay, FR, liliana.cucu@inria.fr

- 3 University of York, GB, rob.davis@york.ac.uk

- 4 VERIMAG Gières, FR, claire.maiza@imag.fr

### — Abstract

This report provides an overview of the discussions, the program and the outcomes of the first Dagstuhl Seminar on Mixed Criticality on Multicore/Manycore Platforms. The seminar brought together researchers working on challenges related to executing mixed criticality real-time applications on multicore and manycore architectures with the main purpose of promoting a closer interaction between the sub-communities involved in real-time scheduling, real-time operating systems / runtime environments, and timing analysis as well as interaction with specialists in hardware architectures.

Seminar March 16–20, 2015 – http://www.dagstuhl.de/15121

**1998 ACM Subject Classification** C.3 Special-purpose and Application-based Systems – Realtime and embedded systems

**Keywords and phrases** Mixed-Criticality, Real-time systems, Multicore/Manycore Platforms, fixed priority; probabilistic scheduling, varying-speed processors, model combination

Digital Object Identifier 10.4230/DagRep.5.3.84

Edited in cooperation with Adriana Gogonel

# 1 Executive Summary

Liliana Cucu-Grosjean Robert I. Davis Claire Maiza Sanjoy K. Baruah

Real-time systems are characterised not only by the need for functional correctness, but also the need for timing correctness. Today, real-time embedded systems are found in many diverse application areas including; automotive electronics, avionics, and space systems. In these areas, technological progress is resulting in rapid increases in both software complexity and processing demands. To address the demand for increased processor performance, silicon vendors no longer concentrate on increasing processor clock speeds, as this approach has led to problems with high power consumption and excessive heat dissipation. Instead, technological development has shifted to multicore processors, with multiple CPUs integrated onto a single chip. The broad technology trend is towards much larger numbers of cores, referred to as manycore, requiring network-on-chip rather than bus interconnects.

Except where otherwise noted, content of this report is licensed

under a Creative Commons BY 3.0 Unported license

Mixed Criticality on Multicore/Manycore Platforms, *Dagstuhl Reports*, Vol. 5, Issue 3, pp. 84–142 Editors: Sanjoy K. Baruah, Liliana Cucu-Grosjean, Robert I. Davis, and Claire Maiza DAGSTUHL Dagstuhl Reports

REPORTS Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

### Sanjoy K. Baruah, Liliana Cucu-Grosjean, Robert I. Davis, and Claire Maiza

Requirements on Size Weight and Power consumption, as well as unremitting cost pressures, are pushing developments in avionics and automotive electronics towards the adoption of powerful embedded multicore processors, with a longer term vision of migrating to manycore. With the adoption of such technology comes the opportunity to combine different applications on the same platform, potentially dramatically reducing assembly and production costs, while also improving reliability through a reduction in harnessing. Different applications may have different criticality levels (e.g. safety-critical, mission-critical, non-critical) designating the level of assurance needed against failure. For example, in automotive electronics, cruise control is a low criticality application, whereas electric steering assistance is of high criticality. In an aerospace context, flight control and surveillance applications in Unmanned Aerial Vehicles are of high and low criticality respectively. The very low acceptable failure rates (e.g.  $10^{-9}$  failures per hour) for high criticality applications imply the need for significantly more rigorous and costly development and verification processes than required by low criticality applications.

Combining high and low criticality applications on the same hardware platform raises issues of time separation and composition; it must be possible to prevent the timing behaviour of high criticality applications from being disturbed by low criticality ones, otherwise both need to be engineered to the same rigorous and expensive standards. Simple methods of achieving this separation, such as time partitioning or allocation to different cores can however be wasteful of processing resources. They may require more expensive hardware than necessary, increasing production costs, which is something industry is strongly motivated to avoid. Time composability is needed so that the timing behaviour of applications, determined in isolation, remains valid when they are composed during system integration. Without time composability integration of complex applications would become infeasible expensive. The transformation of real-time embedded systems into mixed criticality multicore and manycore systems is recognised as a strategically important research area in Europe and the USA.

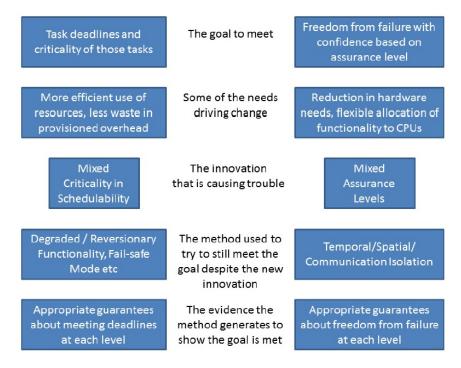

The seminar focused on the two key conflicting requirements of Mixed Criticality Systems: separation between criticality levels for assurance and sharing for resource efficiency, along with the related requirement of time composability. The key research questions addressed were:

- How to provide effective guarantees of real-time performance to applications of different criticality levels via intelligent sharing of resources while respecting the requirements for asymmetric separation / isolation between criticality levels?

- How to provide asymmetric time separation between applications with different levels of criticality so that the impact of lower criticality applications on those of higher criticality can be tightly bounded independent of the behaviour or misbehaviour of the former, without significantly compromising guaranteed real-time performance?

- How to provide time composability for applications of different criticality levels, so that the timing behaviour of applications determined in isolation remains valid when they are composed during system integration?

The sessions of the seminar were structured around a set of themes. Particular attention was given to the interfaces between themes, as these are the areas that can benefit most from improved understanding and collaboration. The discussion groups were organized around the following themes that correspond to research challenges in mixed criticality systems (MCS):

- Platforms and Experimental Evaluation (see Section 5.1);

- Worst-Case Execution Time (see Section 5.2);

- Criticality (see Section 5.3);

- Probabilistic (see Section 5.4).

### Organization of the Seminar

The seminar took place from 15th to 20th March 2015. The first day started with a keynote talk by Prof. Alan Burns (University of York), one of the most influential researchers in the Real-Time Systems field over the last 25 years. Alan reviewed advances in MCS research and underlined current open problems. An overview of his talk is provided in Section 3. The first day ended with presentations and feedback on real implementations (see Section 4) as well as identifying the main themes for group discussion.

The following three days started with presentations, which were followed by discussions either within the identified groups or in an open format.

The second day started with discussions about the motivation for mixed-criticality systems presented by three different participants (see Sections 4.4, 4.5 and 4.6). Different notations are used by different sub-communities and several presentations underlined these differences (see Sections 4.7, 4.8 and 4.9). An outline of the main ideas for probabilistic analysis of real-time systems provided the topics for the discussion group on probabilistic MCS (see Sections 4.10 and 4.11).

The morning of the third day commenced with discussions on the relation between time and MCS (see Section 4.11), which continued into the afternoon's hiking activity.

Starting from the fourth day a slot dedicated to anonymous mixed criticality supporters was added to the program allowing researchers new to the topic to identify open problems in MCS from the perspective of their different domains.

As detailed later in this report, the seminar enabled the real-time community to make important progress in articulating and reaching a common understanding on the key open problems in mixed criticality systems, as well as attracting new researchers to these open problems (see Section 6). The seminar also provided an ideal venue for commencing new collaborations, a number of which are progressing towards new research publications, see Section 7.

The seminar has helped define a research agenda for the coming years that could be supported by follow-up events, given the strong interest expressed by the participants of this seminar.

As organizers, we would like to thank Prof. Reinhard Wilhelm for encouraging us to submit the seminar proposal, Dagstuhl's Scientific Directorate for allowing us to run a seminar on mixed criticality systems, and to the staff at Schloss Dagstuhl for their superb support during the seminar itself. Finally, we would like to thank all of the participants for their strong interaction, presentations, group discussions, and work on open problems, sometimes into the early hours of the morning. We were very pleased to hear about the progress of new found collaborations, and to receive such positive feedback about the seminar itself. Thank you to everyone who participated for a most enjoyable and fruitful seminar.

# 2 Table of Contents

| <b>Executive Summary</b><br>Liliana Cucu-Grosjean, Robert I. Davis, Claire Maiza, and Sanjoy K. Baruah                                         | 84  |

|------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Keynote                                                                                                                                        |     |

| Mixed Criticality – A Personal View<br>Alan Burns                                                                                              | 89  |

| Keynote addenda: An Augmented Model for Mixed Criticality<br>Alan Burns                                                                        | 92  |

| Overview of Talks                                                                                                                              |     |

| Mixed Criticality in Multicore Automotive Embedded Systems<br>Sebastien Faucou                                                                 | 94  |

| Efficiently Safe: Decoding the Dichotomy in Mixed-Criticality Systems <i>Arvind Easwaran</i>                                                   | 95  |

| Adding Cache and Memory Management to the MC <sup>2</sup> (Mixed Criticality on Mul-<br>ticore) Framework<br>James H.Anderson                  | 97  |

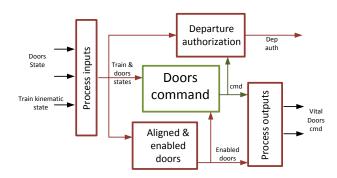

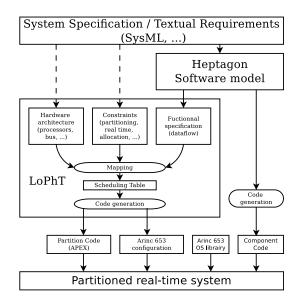

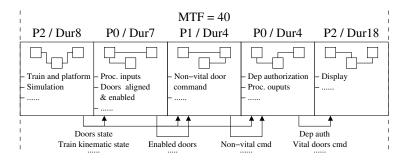

| Mixed-criticality in Railway Systems: A Case Study on Signaling Application<br>A. Cohen, V. Perrelle, D. Potop-Butucaru, E. Soubiran, Z. Zhang | 98  |

| Confidence in Mixed-Criticality Multi-Core<br>Zoë Stephenson amd Mark Pearce                                                                   | 103 |

| Challenges in Mixed Criticality Systems Design – Integration Issues<br>Rolf Ernst                                                              | 105 |

| Real-time Performance Evaluation and VT Control mechanisms for the timing correct use of shared main memory <i>Kai Lampka</i>                  | 106 |

| System-level, Inter-Criticality, Multi-Core Resource Sharing with Scalable Predict-<br>ability                                                 |     |

| Gabriel Parmer       Gabriel Parmer         Mixed Criticality Support on Networks-on-Chip         Leandro Soares Indrusiak                     |     |

| Mapping cricalities to certification levels – a probabilistic attempt<br>Liliana Cucu-Grosjean and Adriana Gogonel                             |     |

| Response Time Analysis for Fixed-Priority Tasks with Multiple Probabilistic Para-<br>meters<br>Dorin Maxim                                     | 113 |

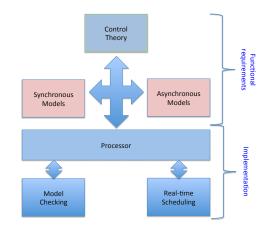

| Viewpoints on the Timing Aspect of Mixed Criticality Systems<br>David Broman                                                                   | 115 |

| Mapping the landscape of mixed criticality systems research<br>Sanjoy K. Baruah                                                                | 116 |

| Some Open Problems in Mixed-Criticality Scheduling <i>Pontus Ekberg</i>                                                                        | 118 |

| Runtime monitoring of time-critical tasks in multi-core systems         Christine Rochange       120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Timing Analysis for Multi/Many-core Platforms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Jan Reineke                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Analysis of pre-emptive systems with caches<br>Sebastian Altmeyer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Using Mixed-Criticality to Reason about Temporal Correctness in Uncertain & Dynamic Environments<br>Nathan Fisher                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Augmenting Criticality-Monotonic Scheduling with Dynamic Processor Affinities         Bjoern B. Brandenburg       124                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Adaptive Uni-processor Fixed Priority Pre-emptive Probabilistic Mixed Criticality<br>Yasmina Abdedda                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| MC Scheduling on Varying-Speed Processors<br>Zhishan Guo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Speedup bounds for multiprocessor scheduling<br>Suzanne van der Ster                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Working Groups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Report on Platforms and Experimental Evaluation         Robert I. Davis       131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Report on WCET      Claire Maiza      Note: N |

| Report on Criticality<br>Sanjoy K. Baruah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Report on Probabilistic Approaches         Liliana Cucu-Grosjean       136                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Open Problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Unification of mixed criticalities, WCET, and probabilistic execution time<br>Enrico Bini                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| New collaborations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Providing Weakly-Hard Guarantees for Mixed-Criticality Systems<br>Robert I. Davis and Sophie Quinton                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| A Multicore Response Time Analysis Framework<br>S. Altmeyer, R. I. Davis, L. Indrusiak, C. Maiza, V. Nelis, and J. Reineke 140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Mixed criticality support for automotive embedded systems<br>Yasmina Abdeddaim, Sébastien Faucou, and Emmanuel Grolleau                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Participants                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# 3 Keynote

### 3.1 Mixed Criticality – A Personal View

Alan Burns (University of York, GB)

License  $\textcircled{\mbox{\scriptsize \ensuremath{\textcircled{} \mbox{\scriptsize only}}}}$ Creative Commons BY 3.0 Unported license  $\textcircled{\mbox{\scriptsize \ensuremath{\mathbb{O}}}}$ Alan Burns

In this talk I want to address four topics:

- The notion of mixed criticality

- A overview of the literature on mixed criticality

- An augmented system model for mixed criticality

- Open Issues in mixed criticality research

The third of these topics is addressed in a separate abstract in Section 3.2. Notes on the other topics are provided below. As this is an extended abstract, derived from a talk, I will not include citations of the many works that have been published on Mixed Criticality. For accurate accrediting of the work alluded to below I refer readers to the Review from York (updated every 6 months and funded by the MCC project) available from: http://www-users.cs.york.ac.uk/~burns/.

It is important to be clear on the notion of 'criticality' as it is used in the, now extensive, literature on mixed critically. To me the notion is primarily based on the consequences and, to some extent, the likelihood of failure. A classification is therefore obtained by some form of hazard (or risk) analysis following a process usually defined in a Standard. All potential hazards much be mitigated during the design and implementation of both the hardware and software architectures. Software components, perhaps implemented within a run-time thread or task, will be assigned a criticality level (although different names are used for this classification in different Standards and application domains). If the late running of a task can contribute to a potential hazard then there must be evidence to support the view that such a deadline miss is sufficient unlikely. Such evidence will come from WCET analysis of the code and scheduling theory. It may also rely on run-time checks and enforcement.

The level of hazard, and the assignment of an assurance, integrity or criticality level will dictates the level of hardware redundancy and the procedures required in the design, verification and implementation of the code. There is considerable cost implications in (justifiable) begin able to reduce the classification of the software within a system.

To me, 'mixed criticality' is a means of dealing with the inherent uncertainty in a complex system. It is a means of providing efficient resource usage in the context of this uncertainty. It is also the means of protecting the more critical work when faults occur; including where assumptions are violated (rely conditions are false).

A mixed critically system is therefore not a mixture of hard and soft deadlines, nor is it a mixture of critical and non-critical components. Moreover it is not only concerned with delivering isolation and non-interference. And it is certainly not about dropping tasks to make a system schedulable. All of these ideas are, I believe, misconceptions about the nature of a mixed criticality system.

So if a mixed criticality approach is a means of dealing with uncertainly, where does this uncertainty come from? The primary source of uncertainly, as recognised in Vestal's initial paper, comes from WCET estimation. We know that WCET cannot be known with certainty. All estimates have a probability of being wrong (too low). But all estimates are attempting to be safe (pessimistic). In particular C(LO) is a valid engineered estimate with

the belief that  $C(LO) > WCET^1$ . Beliefs can be misplaced of course, which is why systems must be built to be resilient in the face of faults. But there must be a high level of confidence, perhaps expressed as a probability, that the assertion C(LO) > WCET is true.

Other forms of uncertainty can come from the environment of the system. An event driven system must make assumptions about the intensity of the events it must deal with (in a timely fashion). Again this cannot be known with certainty. So the 'Load' parameters (however they may appear in the scheduling analysis) need to be estimated (safely). In particular, the minimum arrival interval (T) for a sporadic task (i.e. the assumed minimum interval between two events from the same source) as assumed at even the lowest criticality level of the system much be safe, that is T(LO) < T(real).

Critical systems need to demonstrate survivability. Faults will occur and some level must be tolerated. One source of faults is that relate to the assumptions upon which the verification of the timing behaviour of the system was based eg. WCET, arrival rates, etc. A common notion in the fault tolerance literature is the idea of a fault model. Fault models provide a means of assessing/delivering survivability. For example:

- full functional behaviour with a certain level of faults;

- Graceful Degradation for more severe faults.

Graceful Degradation is a controlled reduction in functionality, aiming to preserve safety. So within the mixed criticality domain: if any task executes for more than C(LO) and all HI-criticality tasks execute for no more than C(HI) then it can be demonstrated that all HI-criticality tasks meet their deadlines.

As a strategy for Graceful Degradation a number of schemes in Mixed Criticality literature have been proposed:

- Drop all lower critical work

- **D**rop some, using notions of importance etc.

- Extend periods and deadlines (elastic task model)

- Reduce functionality within low and high criticality tasks

This strategy should perhaps be extended to issues concerning the C(HI) bound also being wrong!

If tasks are dropped/aborted then this cannot be arbitrary – the approach must be related back to the software architecture and task dependencies. So if task A is closely coupled to task B then either drop both or neither. Recovery must also relate to the needs of the software (e.g. dealing with missing/stale state).

What I want to emphasis with the above discussion is that the dropping of functions can never be seen as part of the normal behaviour of the system. That would not be acceptable to any system's developer. Rather it is a means of protected the most critically functions during a system overload, which itself is due to a fault, with may occur due to the inherent uncertainly in the system's behaviour and environment.

Another issue that arises in the mixed criticality literature is the use of a 'criticality mode' to capture the behaviour of the system when all functions are being deliver, and other modes that relates to reduced functionality. We have tended to call these modes (in a dual-criticality system) LO-criticality mode when all is well, and HI-criticality mode when only HI-criticality functions are guaranteed. This terminology is I feel misleading, the normal behaviour of the system when all functions are timely should be called 'normal'.

<sup>&</sup>lt;sup>1</sup> Many papers on mixed criticality assume two critically levels, LO and HI, and two estimates of WCET related to these two levels: C(LO) and C(HI), with  $C(LO) \leq C(HI)$ .

### Sanjoy K. Baruah, Liliana Cucu-Grosjean, Robert I. Davis, and Claire Maiza

After a fault, and degraded functionality it should be possible for the system to return to full functionality (i.e. normal mode). After all, a 747 can fly with 3 engines, but its nice to get the 4th one back. Fault recovery is therefore also an issue for mixed criticality behaviour. Indeed, as I have tried to explain, much of the work on mixed criticality systems need to be more cognisant of the available literature on fault tolerance.

Since Vestal's paper there has been at least 180 articles published (one every 2 weeks!). Some top level observations follow. For uniprocessors:

- For FPS, AMC seems to be the 'standard' approach.

- For EDF, schemes that have a virtual deadline for the *HI*-criticality tasks seem to be standard.

- Server based schemes have been revisited.

- Not too much work on the scheduling schemes actually used in safety-critical systems, e.g. cyclic executives and non-preemptive (or cooperative) FPS.

For multiprocessor systems there are a number of schemes (extensions from uni-criticality systems). Similarly for resource sharing protocols. Work on communications is however less well represented. As indicated above, there is lots of work on graceful degradation (although few papers use that term).

Almost all papers stick to just two criticality levels. But remember LO-criticality does not mean no-criticality! Some papers pay lip service to multiple levels, but not many. It is still not clear what is the model we require for, say, 4 or 5 levels? To me it does not seem to make sense to have five estimates of WCET.

Notwithstanding the obvious synagy with fault tolerance there is actually little work on linking mixed criticality to fault tolerance in general. There is also little work on probabilistic assessment of uncertainty. There is some implementation work, but arguable not enough. Similarly, there is some comparative evaluations, but again not enough. There is however good coverage of formal issues such as speed-up factors.

I will finish by recording the open issues that I have identified from reading the extensive mixed criticality literature.

- 1. As well as looking at mixing criticality levels within a single scheduling scheme (e.g. different priorities within FPS) we need to look at integrating different schemes (e.g. Cyclic Executives for safety-critical, FPS for mission critical on the same processor).

- 2. More work is needed to integrate the run-time behaviour (monitoring and control) with the assumptions made during static verification.

- 3. We need to be more holistic in terms of ALL system resources (especially communications media).

- 4. There are a number of formal aspects of scheduling still to be investigated.

- 5. We need to be sure that techniques scale to at least 5 levels of criticality.

- 6. There are still a number of open issues with regard to graceful degradation and fault recovery.

- 7. There is little work as yet on security as an aspect of criticality.

- 8. We need protocols for information sharing between criticality levels.

- 9. We need better WCET analysis to reduce the (safe) C(HI) and C(LO) values (or at least improve our confidence in the numbers used).

- 10. We should look to have an impact on the Standards relevant to the application domains we hope to influence.

- 11. Better models for system overheads and task dependencies are needed.

- 12. How many criticality levels to support (and how many estimates of the sources of uncertainty to accommodate)?

- 13. We do not as yet have the structures (models, methods, protocols, analysis etc) that allow tradeoffs between sharing and separation to be evaluated.

To conclude, the Dagstuhl seminar is both timely and necessary in moving our research forward.

### 3.2 Keynote addenda: An Augmented Model for Mixed Criticality

Alan Burns (University of York, GB)

Inevitably not all papers on mixed criticality have used the same system or task model. But following on from the initial paper of Vestal [1] the most common form of the mixed criticality model is one that has a small number of criticality levels and that for each level tasks have an assigned estimation of worst-case execution time (WCET), C. Early publications on mixed criticality have often further restricted the model to have just two criticality levels, HI and LO, and therefore only two computations parameters C(HI) and C(LO). As we move back to using four or five criticality levels then the question arises – do we really have this number of ways of estimating WCET?

A criticality level determines many aspects of how a software function, embedded in a run-time task, is to be produced and verified. But it does not follow that distinct means of estimating or measuring execution time are available at each criticality level. In this short note we argue that two estimates are sufficient for a suitably expressive model to be defined.

Assume that the application domain of the defined system has four levels of criticality: A, B, C, D (with A being the highest level) and one non-critical level E. Code in E, if it exists, will have no or soft deadlines and not be crucial for any function of the system. Nevertheless, it may include house-keeping functions that are useful and should be executed if possible.

Level D is the lowest criticality level. We term this the *normal* mode of the system in that during normal, fault-free, execution all code from all four criticality levels are guaranteed to meet defined timing constraints. To validate normal behaviour it is necessary for all critical code to have an estimate of its WCET that is appropriate for level D criticality. We call these estimates C(normal) – in existing literature this would be called C(D).

As code of a particular criticality level has to be produced and verified to the standard dictated by the assigned level, there must be an estimate of WCET that is linked to that criticality level. So level A has a C(A) estimate, level B a C(B) estimate etc. In general, we can say that all critical code has an estimate commensurate with its own criticality, we term this C(self).

To summarise, all task have two estimates of WCET: C(self) and C(normal), with  $C(self) \ge C(normal)$ . For tasks of the lowest level of criticality (level D in our framework), these two estimates are the same.

The run-time behaviour of our system, following the basic idea of Vestal, is as follows:

- If all critical tasks execute for no more than their C(normal) values then all critical deadlines are met.

- All tasks are prevented, by run-time monitoring, to execute for more than C(self).

- If any task of criticality level X executes for more than C(normal) then all tasks of critically level X and higher must continue to meet their deadlines, using estimates of WCET of C(self) for tasks of criticality X and C(normal) for tasks of criticality higher than X.

### Sanjoy K. Baruah, Liliana Cucu-Grosjean, Robert I. Davis, and Claire Maiza

In the above scenario, tasks of criticality levels below X are no longer guaranteed (and may be subject to forms of graceful degradation necessary to ensure the continuing correct execution of levels X and higher).

Note that this is a different behaviour from the one used by AMC [2], for example. In that protocol the second case would use estimates of C(X) for the higher criticality tasks (not C(normal)). Of course the augmented model presented here can be directly expressed in the original Vestal model if all intermediate estimates of WCET between C(normal) and C(self) are assigned the same value as C(normal).

As well as simplifying the model, the above behaviour is supported by at least some industrial practice. Code of level A is likely to be subject to coding standards that restrict the expressive power of the programming language employed. For example, recursion may be prohibited as may the arbitrary use of pointers and 'while' loops. It follows that level A code is more predictable and less likely to execute for more than C(normal).

This augmented model is motivated by the fact that software development processes are unlikely to deliver more than two estimates of WCET. However, this does not mean that run-time behaviour cannot use computed estimates that facilitate more fine-grain control over graceful degradation. For example, if a task of level A executed for more than C(self) (i.e. C(A)) then the above model will allow all tasks of all lower criticality levels to be abandoned (to ensure level A work is preserved). However a Real-Time Systems engineer could quite reasonable argue that this reaction is overly conservative. It would be quite straightforward to use the scheduling analysis to compute a value of C(C), with C(self) > C(C) > C(normal), and enforce the run-time behaviour: if a level A task executes for more than C(normal) but no higher than C(C) then only tasks of level D need to degrade. Sensitivity analysis for fixed priority scheduling has already been used [3] to solve a related problem.

This useful step, of computing intermediate WCET estimates, does not however detract from the application model being advocated here. This model restricted the number of external/given estimates of WCET to two.

Vestal [1], and much follow on work, has focused on WCET as the main source of uncertainty in the model of the system. Other forms of uncertainly exist – including load from the environment, faults in the hardware, power from (perhaps unreliable) sources etc. For all of these sources of uncertainty we argue that there should be two estimates. One for the normal all inclusive criticality of the system and one that reflects the particular criticality of the component.

### References

- 1 S. Vestal. Preemptive scheduling of multi-criticality systems with varying degrees of execution time assurance. In *Proc. of the IEEE Real-Time Systems Symposium (RTSS)*, pages 239–243, 2007.

- 2 S.K. Baruah, A. Burns, and R. I. Davis. Response-time analysis for mixed criticality systems. In *Proc. IEEE RTSS*, 2011, pages 34–43.

- **3** T. Fleming and A. Burns. Incorporating the notion of importance into mixed criticality systems. In L. Cucu-Grosjean and R. I. Davis, editors, *Proc. 2nd Workshop on Mixed Criticality Systems (WMC)*, *RTSS*, 2014, pages 33–38.

Mixed-criticality needs feedback from real implementation

### 4.1 Mixed Criticality in Multicore Automotive Embedded Systems

Sebastien Faucou (University of Nantes, FR) sebastien.faucou@univ-nantes.fr

$\begin{array}{c} \mbox{License} \ensuremath{\textcircled{@}} \ensuremath{\textcircled{@}} \ensuremath{\textcircled{C}} \ensuremath{\textcircled{@}} \ensuremath{\textcircled{C}} \ensuremath{\textcircled{@}} \ensuremath{\textcircled{C}} \ensuremath{\textcircled{@}} \ensuremath{@} \ensu$

### Introduction

The automotive industry pursues an effort toward the standardization of in-vehicle embedded systems technologies. If we focus on the topics of interest of this seminar, two standards stands out: ISO 26262, the functional safety standard; and AUTOSAR OS, the RTOS component of the standardized AUTOSAR architecture. Studying these standards gives some insight on the way mixed criticality is handled today in automotive embedded systems and allows to identify direction for future works.

### ISO 26262: ASIL and freedom from interference

ISO 26262 defines two key concepts. The first one is the risk classification scheme composed of four *ASILs* (Automotive Safety Integrity Level) that range from A (the least critical) to D (the most critical). ASILs are attached to hazardous events and mapped to software components as a result of the hazard analysis. Mixed criticality requirements arise when the software components of a system have different ASILs.

The second key concept of ISO 26262 is *freedom from interference*. Freedom from interference is established when no error can propagate from low-criticality components to high criticality components. Freedom from interference does not implies full isolation but rather that interferences between criticality classes are bounded. It encompasses functional and extra-functional concerns, including timeliness and communication. In a system built on top of a shared platform, if freedom from interference can not be proved, then every component shall be designed with the requirements associated with the highest ASIL among all the co-hosted components.

### AUTOSAR OS

AUTOSAR OS extends OSEK/VDX OS with several features, including *protection facilities* and support for multicore platforms. Among the protection facilities, timing protection monitors the run-time behaviour of the jobs, assuming a sporadic model. This allows to use for instance the schedulability tests developed for Vestal's model [1] and may be for some of its extensions [2] in order to validate the capacity of the system to survive to timing faults and preserve the timeliness of its most critical functions, *ie.* establishing freedom from interference in the time domain.

Protection facilities also include the possibility to partition the memory and the peripherals of the platforms between *OS-Applications* (set of tasks, interrupt handlers and shared resources) and to enforce this partitionning at run-time. These features contribute to freedom from interference in the communication domain

### MC in multicore automotive embedded systems

The two parts of AUTOSAR OS protection facilities presented above are usefull but with the advent of multicore platforms, this is not sufficient. Indeed, these mechanisms do not adress the management of shared hardware resources in a mixed-criticality context. Examples of shared hardware resources include the memory bus, the SRAM banks, the shared cache level found in high-ends microcontroller for infotainment. These shared resources are channels that allow low criticality tasks to interfere on the execution of highest criticality ones.

### Two directions for futures works

Vestal's model and its extensions offer a solid theory for real-time scheduling of mixed criticality systems. Some works have been carried on in order to evaluate the pertinence of this theory in the context of Linux-based el-time ystems [3]. The same type of works remains to be done in the context of smaller (embedded) real-time systems, taking into account and exploiting some distinctive features such as: limited hardware resources, static software, sub-millisecond deadlines, etc.

According to the current state of the art, the second direction that should be considered a priority is the design of methods to bound interferences in multicore systems. Once again, the distinctive features of automotive embedded systems should be exploited to propose low footprint mechanisms, amenable to static analysis.

### References

- 1 S. Vestal. Preemptive scheduling of multi-criticality systems with varying degrees of execution time assurance. In *Proc. of the IEEE Real-Time Systems Symposium (RTSS)*, pages 239–243, 2007.

- 2 S.K. Baruah, A. Burns, and R. I. Davis. Response-time analysis for mixed criticality systems. In *Proc. IEEE RTSS*, 2011, pages 34–43.

- 3 Huang-Ming Huang, Christopher D. Gill, and Chenyang Lu. Implementation and evaluation of mixed-criticality scheduling approaches for periodic tasks. In *RTAS*, pages 23–32, 2012.

## 4.2 Efficiently Safe: Decoding the Dichotomy in Mixed-Criticality Systems

Arvind Easwaran (Nanyang Technological University, SG) arvinde@ntu.edu.sg

License  $\textcircled{\mbox{\scriptsize \ensuremath{\textcircled{} \ensuremath{\hline{} \ensuremath{\textcircled{} \ensuremath{\textcircled{} \ensuremath{\textcircled{} \ensuremath{\hline{} \ensuremath{\hline{} \ensuremath{\hline{} \ensuremath{\hline{} \ensuremath{\hline{} \ensuremath{\\} \ensuremath{\hline{} \ensuremath{\\} \ensuremath{\textcircled{} \ensuremath{\\} \ensuremath{\} \ensuremath{\\} \ensuremath{\\} \ensuremath{\\} \ensuremat$

An increasing trend in embedded systems is towards open computing environments, where multiple functionalities are developed independently and integrated together on a single computing platform. This trend is evident in industry-driven initiatives such as ARINC653 Integrated Modular Avionics (IMA) in avionics and AUTOSAR in automotive. An important notion behind this trend is the safe partitioning of separate functionalities, primarily to achieve fault containment. This raises the challenge of how to balance the conflicting requirements of partitioning for safety assurance and efficient resource sharing for economical benefits. The concept of *mixed-criticality*, first introduced by Vestal [1], appears to be important in meeting these dichotomous goals.

96