Leibniz Transactions on **Embedded Systems**

Volume 5 | Issue 1 | October 2018

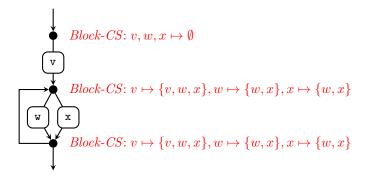

## **ISSN 2199-2002**

#### Published online and open access by

the European Design and Automation Association (EDAA) / EMbedded Systems Special Interest Group (EMSIG) and Schloss Dagstuhl – Leibniz-Zentrum für Informatik GmbH, Dagstuhl Publishing, Saarbrücken/Wadern, Germany.

Online available at

http://www.dagstuhl.de/dagpub/2199-2002.

## Publication date October 2018

# Bibliographic information published by the Deutsche Nationalbibliothek

The Deutsche Nationalbibliothek lists this publication in the Deutsche Nationalbibliografie; detailed bibliographic data are available in the Internet at http://dnb.d-nb.de.

#### License

This work is licensed under a Creative Commons Attribution 3.0 Germany license (CC BY 3.0 DE): http: //creativecommons.org/licenses/by/ 3.0/de/deed.en.

In brief, this license authorizes each and everybody to share (to copy,

distribute and transmit) the work under the following conditions, without impairing or restricting the authors' moral rights:

Attribution: The work must be attributed to its authors.

The copyright is retained by the corresponding authors.

#### Aims and Scope

LITES aims at the publication of high-quality scholarly articles, ensuring efficient submission, reviewing, and publishing procedures. All articles are published open access, i.e., accessible online without any costs. The rights are retained by the author(s).

LITES publishes original articles on all aspects of embedded computer systems, in particular: the design, the implementation, the verification, and the testing of embedded hardware and software systems; the theoretical foundations; single-core, multi-processor, and networked architectures and their energy consumption and predictability properties; reliability and fault tolerance; security properties; and on applications in the avionics, the automotive, the telecommunication, the medical, and the production domains.

### Editorial Board

- Alan Burns (Editor-in-Chief)

- Bashir Al Hashimi

- Karl-Erik Arzen

- Neil Audsley

- Sanjoy Baruah

- Samarjit Chakraborty

- Marco di Natale

- Martin Fränzle

- Steve Goddard

- Gernot Heiser

- Axel Jantsch

- Florence Maraninchi

- Sang Lyul Min

- Lothar Thiele

- Virginie Wiels

Editorial Office Michael Wagner (Managing Editor) Jutka Gasiorowski (Editorial Assistance) Dagmar Glaser (Editorial Assistance) Thomas Schillo (Technical Assistance)

Contact Schloss Dagstuhl – Leibniz-Zentrum für Informatik LITES, Editorial Office Oktavie-Allee, 66687 Wadern, Germany lites@dagstuhl.de http://www.dagstuhl.de/lites

Digital Object Identifier 10.4230/LITES-v005-i001

# **Contents**

| Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions<br>Bader Naim Alahmad and Sathish Gopalakrishnan | 1:1-1:30 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------|

| Errata for Three Papers (2004-05) on Fixed-Priority Scheduling with                                                               |          |

| Self-Suspensions                                                                                                                  |          |

| Konstantinos Bletsas, Neil C. Audsley, Wen-Hung Huang, Jian-Jia Chen, and<br>Geoffrey Nelissen                                    | 2:1-2:20 |

| The Semantic Foundations and a Landscape of Cache-Persistence Analyses<br>Jan Reineke                                             | 3:1-3:52 |

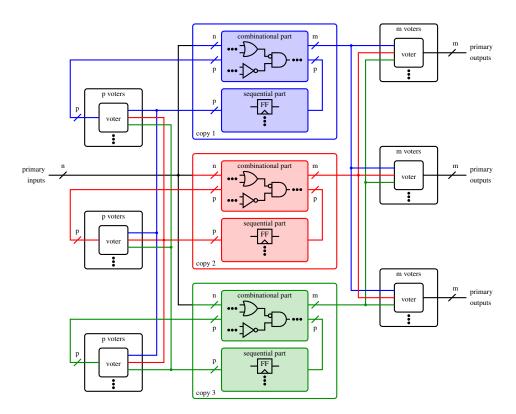

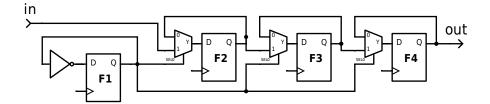

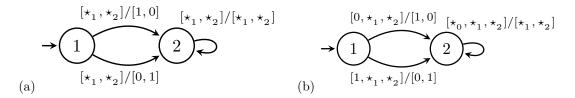

| A Static Analysis for the Minimization of Voters in Fault-Tolerant Circuits<br>Dmitry Burlyaev, Pascal Fradet, and Alain Girault  | 4:1-4:26 |

# **Risk-Aware Scheduling of Dual Criticality Job** Systems Using Demand Distributions

## Bader Naim Alahmad

The University of British Columbia 2366 Main Mall, Vancouver, BC, Canada V6T 1Z4 bader@ece.ubc.ca https://orcid.org/0000-0002-6409-1277

## Sathish Gopalakrishnan

The University of British Columbia 2332 Main Mall, Vancouver, BC, Canada V6T 1Z4 sathish@ece.ubc.ca

## — Abstract -

We pose the problem of scheduling Mixed Criticality (MC) job systems when there are only two criticality levels, LO and HI-referred to as Dual Criticality job systems—on a single processing platform, when job demands are probabilistic and their distributions are known. The current MC models require that the scheduling policy allocate as little execution time as possible to Lo-criticality jobs if the scenario of execution is of HI criticality, and drop Lo-criticality jobs entirely as soon as the execution scenario's criticality level can be inferred and is HI. The work incurred by "incorrectly" scheduling Lo-criticality jobs in cases of HI realized scenarios might affect the feasibility of HI criticality jobs; we quantify this work and call it Work Threatening Feasibility (WTF). Our objective is to construct online scheduling policies that minimize the expected WTF for the given instance, and under which the instance is feasible in a probabilistic sense that is consistent with the traditional deterministic definition of MC feasibility. We develop a probabilistic framework for MC

scheduling, where feasibility is defined in terms of (chance) constraints on the probabilities that Lo and H<sub>I</sub> jobs meet their deadlines. The probabilities are computed over the set of sample paths, or trajectories, induced by executing the policy, and those paths are dependent upon the set of execution scenarios and the given demand distributions. Our goal is to exploit the information provided by job distributions to compute the minimum expected WTF below which the given instance is not feas*ible in probability*, and to compute a (randomized) "efficiently implementable" scheduling policy that realizes the latter quantity. We model the problem as a Constrained Markov Decision Process (CMDP) over a suitable state space and a finite planning horizon, and show that an optimal (non-stationary) Markov randomized scheduling policy exists. We derive an optimal policy by solving a Linear Program (LP). We also carry out quantitative evaluations on select probabilistic MC instances to demonstrate that our approach potentially outperforms current MC scheduling policies.

2012 ACM Subject Classification Mathematics of computing  $\rightarrow$  Markov processes, Software and its engineering  $\rightarrow$  Real-time systems software, Software and its engineering  $\rightarrow$  Real-time schedulability Keywords and Phrases Real-time scheduling; Mixed-criticality; Probability distribution; Chanceconstrained Markov decision process; Linear programming Digital Object Identifier 10.4230/LITES-v005-i001-a001

Received 2016-02-04 Accepted 2018-01-07 Published 2018-05-30

#### 1 Introduction

We consider a system comprised of a *finite set of jobs* executing upon a *shared platform* (processor), and a *scheduling policy* that allocates processor time to jobs. A Mixed-Criticality (MC) real-time job system is one that carries out multiple jobs, with each job being of a specific criticality. For example, in an avionics/UAV system, some jobs relate to the flight stability or safety of the aircraft,

© Bader Naim Alahmad and Sathish Gopalakrishnan:

licensed under Creative Commons Attribution 3.0 Germany (CC BY 3.0 DE)

Leibniz Transactions on Embedded Systems, Vol. 5, Issue 1, Article No. 1, pp. 01:1-01:30

Leibniz Transactions on Embedded Systems

LEIDHIZ TRANSACLIONS ON EMIDEQUED Systems LITES Schloss Dagstuhl – Leibniz-Zentrum für Informatik, Dagstuhl Publishing, Germany

## 01:2 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

and these jobs have the highest criticality. Other jobs may relate to the mission of the aircraft (gather visual information of a particular region) and these jobs may be of a lower criticality. In the special and important case—that we consider in this article—where every job assumes one of exactly two criticality levels, LO or HI, we will refer to the MC system as Dual-Criticality.

From a *job scheduling* perspective, one would like to schedule jobs so that they meet their timing constraints or deadlines. To do so, one needs to know the execution time requirements of these jobs. Using worst-case execution time (WCET) estimates for execution time would lead to infeasibility of low criticality jobs (because the worst-case utilization could saturate the system capabilities) but, since worst-case execution times are rarely realized, one could use the same platform for jobs of all criticality levels provided the scheduler makes suitable choices when the execution duration of a job approaches the worst case or when it exceeds certain thresholds.

Vestal [38] was the first to offer an abstraction for scheduling MC job systems. In Vestal's model, there are  $L \ge 2$  distinct criticality levels, and n jobs  $J_1, \ldots, J_n$ . For notational convenience, we denote as [n] the set  $\{1, \ldots, n\}$  for integers  $n \ge 1$ . Job  $J_i$  is characterized by the parameters  $(\chi_i, c_i, d_i)$ , where

•  $\chi_i \in [L]$  is job  $J_i$ 's criticality;

c<sub>i</sub> = (c<sub>i</sub>(1),...,c<sub>i</sub>(L)) ∈ (0,∞)<sup>L</sup> is the vector of WCET estimates at all criticality levels;

d<sub>i</sub> > 0 is job J<sub>i</sub>'s deadline.

For example, consider a triple-criticality MC job system consisting of three jobs  $J_1$ ,  $J_2$ , and  $J_3$  with criticalities  $\chi_1 = 1$ ,  $\chi_2 = 3$ , and  $\chi_3 = 2$ , respectively, and with the following WCET estimates:

$$J_1: \quad c_1 = (c_1(1) = \mathbf{90}, c_1(2) = 90, c_1(3) = 90)$$

$$J_2: \quad c_2 = (c_2(1) = 10, c_2(2) = 12, c_1(3) = \mathbf{20})$$

$$J_3: \quad c_3 = (c_3(1) = 1, c_3(2) = \mathbf{500}, c_3(3) = 500).$$

We shall make the following common monotonicity assumption:  $c_i(1) \leq \cdots \leq c_i(L)$  for every  $i \in [n]$ . Moreover, we will assume that  $c_i(\ell) = c_i(\chi_i)$  for all  $\ell \geq \chi_i$ , so that it is sufficient to specify job  $J_i$ 's WCET estimates by giving  $c_i(1), \ldots, c_i(\chi_i), i \in [n]$ . An execution scenario, or behavior, is a particular realization of job demands in a particular run of the system; i.e., it is a vector  $b = (b_1, \ldots, b_n)$  in  $\prod_{i=1}^n (0, c_i(\chi_i)]$ . In our example, (10, 11, 450) is a possible execution scenario. In any particular run of the system, the scenario remains unknown until *all* jobs finish execution. The criticality level of behavior b is defined as

$$\mathsf{critDemand}(b) = \min\{\ell \in [L] : b_i \le c_i(\ell) \quad \forall i \in [n]\}.$$

For instance, critDemand((10, 11, 450)) = 2. During a schedule, at time t, say, job  $J_i$  is said to be **operating** at criticality level  $\ell \in [L]$  if it has been given at least  $c_i(\ell - 1)$  but less than  $c_i(\ell)$ units of execution, and has not finished execution at time t. We call this time-dependent quantity the **job's operational criticality level** at t. With the monotonicity assumption, the range of execution times that job  $J_i$  might demand when operating at criticality level  $\ell$  is the open interval  $(c_i(\ell - 1), c_i(\ell)]$ , with the convention that  $c_i(0) = 0$ . In our example, if we take a snapshot of a certain schedule at, say time 63, and observe that jobs  $J_1$ ,  $J_2$  and  $J_3$  have executed for 50, 10 and 3 time units, respectively, but  $J_2$  has not yet finished execution, then  $J_2$ 's operational criticality level at time 63 is 2. However, if  $J_2$  finishes execution at time 63 with 10 time units of execution, then its operational criticality level for all  $t \leq 63$  is 1. The operational criticality level remains the same from time t until  $J_i$  either signals that it has finished execution, or it executes for  $c_i(\ell)$  time unit at some t' > t and does not signal completion, at which point its operational criticality level jumps to  $\ell + 1$ . As such, a job's operational criticality level is an increasing piecewise-constant function of time, demand, and the scheduling policy, with a (random) set of jump points.

At time t, the maximum of all job operational criticality levels is the **system operational criticality level** at time t. We note that the system operational criticality level of an observed allocation snapshot, say b, at some time, is not the same as critDemand(b); the system operational criticality level depends on additional information not encoded in b, namely whether or not jobs finished execution, whereas critDemand(b) assumes that all jobs finished execution. Since the system operational criticality level is defined in terms of the job operational criticality levels, the former is also an increasing piecewise-constant function. In our example, the system operational criticality level at time 63 with the same execution snapshot (50, 10, 3) is 1 if  $J_2$  finishes execution at or before time 63, and is 2 otherwise. If the scheduler selects  $J_2$  to execute from time 63 to time 67, then at time 65, the system operational critical level makes a jump from 2 to 3 (since then  $J_2$  has executed for  $12 = c_2(2)$  time units and has not finished execution), and remains 3 until the end of the schedule.

Once a job signals that it has finished execution, its **demand** is realized. A demand realization is a scenario of execution. Every job demand realization maps naturally to a unique **job criticality level realization**, and the maximum of which across all jobs is the **system criticality level realization**. Different runs, or executions, of the input job system might yield different criticality level realizations, since, generally, a job might demand anything in  $(0, c_i(\chi_i)]$ , and job demand realizations might differ across different executions.

## The Job Dropping Model: Literature and Optimality

In addition to Vestal [38], there has been a substantial body of work that analyzes scheduling policies for deterministic MC systems, wherein low(er) criticality jobs are dropped when a high(er) criticality job demands more execution time. One such approach was studied by Baruah et al. [8, 10]. In this approach, low criticality jobs are dropped when it is deemed necessary to allocate more time to a high criticality job. This decision is based on deterministic thresholds and is conservative in the sense that worst-case assumptions are made about the execution time requirements of the low criticality jobs and other high criticality jobs. As a consequence, low criticality jobs may miss deadlines even when it may be possible to meet the deadlines for high and low criticality jobs. Feasibility of a given Dual-Criticality instance in this model is defined as follows: For every scenario of execution, if the scenario's criticality level is LO, all jobs should be given enough execution time to complete entirely and should meet their deadlines, but if the scenario's criticality level is HI, only HI-criticality jobs need to be given execution budget and must complete before their deadlines. In the latter case, giving any execution time to LO-criticality jobs is considered as an erroneous allocation, and doing so negatively affects the achievable processor utilization.

A non-clairvoyant, or online, scheduling policy does not know the scenario of execution in advance, and only an omniscient clairvoyant policy knows the realized scenario at time 0, and is therefore able to decide whether or not to drop Lo-criticality jobs at the beginning of system operation and thus achieve the maximum processor utilization. An instance  $I = (J_1, \ldots, J_n; L)$  is said to be **correctly MC-schedulable** by scheduling policy  $\pi$  if for every scenario (behavior)  $b \in \prod_{i=1}^{n} (0, c_i(\chi_i)]$ , if b has criticality level  $\ell$ , then every  $J_i$  with  $\chi_i \geq \ell$  can be given  $b_i$  units of execution during  $[0, d_i]$  under  $\pi$ . An instance I is said to be **MC-feasible** if there is an *online* scheduling policy under which I is correctly MC-schedulable.

Baruah et al. [10] showed that checking MC-feasibility can be reduced to checking its defining condition only for the scenarios that assume the WCET estimates; i.e., for  $b \in \{(c_1(\ell_1), \ldots, c_n(\ell_n)) : \ell_i \in [\chi_i]\}$ . The MC-feasibility problem was shown to NP-Hard in the strong sense [7]; however, it is not yet clear whether or not MC-feasibility belongs to the class NP.

If an instance I is not MC-feasible, then there is no online scheduling policy under which it is correctly MC-schedulable. Conversely, if instance I is MC-feasible, then an online scheduling policy that correctly MC-schedules I may or may not exist.

## 01:4 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

A widely used measure of the performance of non-clairvoyant MC-scheduling policies is the processor **speed-up factor** (Baruah et al. [8], Kalyanasundaram and Pruhs [30]). It is defined as follows: If  $\pi$  is a non-clairvoyant scheduling policy, then its speed-up factor is the smallest real number s > 1 such that, for *every* MC instance I, if I is MC-feasible on a unit-speed processor, then policy  $\pi$  will correctly MC-schedule I on an s (or more)-speed processor. An **optimal** policy is one that minimizes s.

In the MC context, a non-unit speed-up factor arises because of the following: A non-clairvoyant algorithm has only WCET estimates available, and it does not know the scenario of execution in advance, so in high criticality scenarios, the algorithm might allocate execution time to jobs whose criticality is less than the realized system criticality level. Thus the earlier the time at which the scenario's criticality level is inferred under the scheduling policy while preserving feasibility (in the MC sense), the less the "processor time waste" the policy incurs for that scenario. Since the scheduler can drop all Lo-criticality jobs as soon as the scenario's criticality is inferred as HI. predicting the earliest such time plays a central role in the MC-scheduling problem. Given an MC job instance, a scenario of execution and a non-clairvoyant scheduling policy, we call the earliest time instant at which the execution scenario's criticality level is inferred with certainty the **Time** of Criticality Inference  $(T_{CI})$  associated with the scheduling policy for the given scenario. Giving any execution time to LO-criticality jobs early on in the schedule will only delay the  $T_{\rm CI}$ . and thus delay the time instant at which we can decide whether or not to drop Lo-criticality jobs. However, to preserve the schedulability of Lo-criticality jobs in case the scenario is of Lo criticality, the policy must judiciously give execution time to Lo-criticality jobs early on in the schedule. Thus, we are facing conflicting objectives, and the optimal scheduling policy must strike the right allocation balance.

Here is an example to illustrate the situation.

**Example 1.** Consider a dual-criticality MC job system consisting of two jobs  $J_1$  and  $J_2$  with the following parameters:

$$J_1: \quad c_1 = (c_1(\text{LO}) = 200, c_1(\text{HI}) = 300), \quad \chi_1 = \text{HI}, \quad d_1 = 450$$

$$J_2: \quad c_2 = (c_2(\text{LO}) = 250), \qquad \qquad \chi_2 = \text{LO}, \quad d_2 = 300.$$

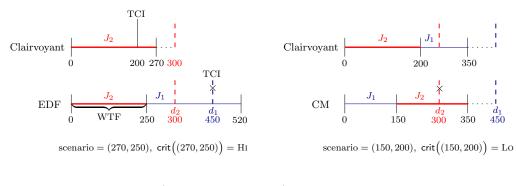

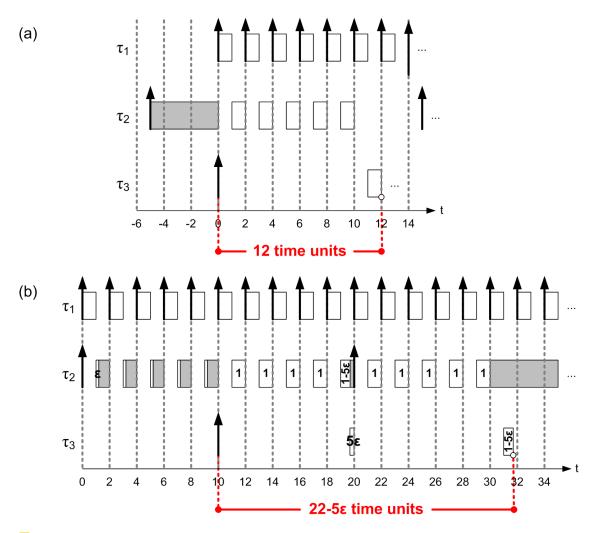

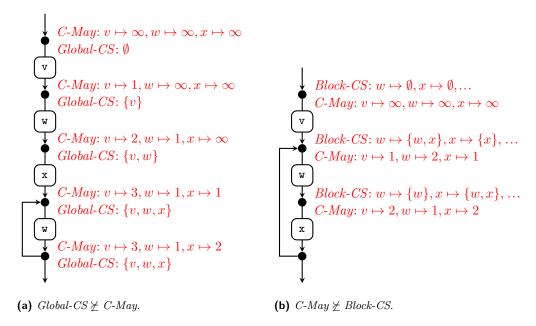

First let us examine how the clairvoyant algorithm would MC-schedule this job instance. If the scenario is of HI criticality, then the clairvoyant policy knows this at time 0 and drops  $J_2$  entirely and schedules  $J_1$ , which would then meet its deadline of 450. If the scenario is of LO criticality, then the clairvoyant policy schedules both  $J_1$  and  $J_2$  using the Earliest Deadline First (EDF) policy, and they both meet their deadlines: The worst-case LO-criticality scenario is (200, 250), and under EDF,  $J_2$  is scheduled first and finishes at time  $250 < d_2 = 300$ , and then  $J_1$  occupies the processor till time  $450 (= d_1)$ . Now we consider two non-clairvoyant scheduling policies (see Figure 1):

- **EDF.** Suppose that the scenario of execution is (270, 250), which has HI criticality. EDF first schedules  $J_2$  up to time 250, and then selects  $J_1$  to occupy the processor until time 520. At time 450, however,  $J_1$  misses its deadline.

- Criticality Monotonic (CM), which is a fixed-priority scheduling policy that at each instant schedules, among the jobs that have not finished execution, the job with the highest criticality. Suppose that the scenario of execution is the Lo-criticality (150, 200).  $J_1$  occupies the processor from time 0 to time 150, then  $J_2$  executes until time 350.  $J_2$ , however, misses its deadline at time 300.

The problem with EDF is that it does not consider criticalities, and consequently, in our example, it scheduled  $J_2$  when it should have dropped it altogether. The work done by  $J_2$  affected

$J_1 : c_1 = (c_1(\text{Lo}) = 200, c_1(\text{HI}) = 300), \quad \chi_1 = \text{HI}, \quad d_1 = 450$  $J_2 : c_2 = (c_2(\text{Lo}) = 250), \qquad \qquad \chi_2 = \text{Lo}, \quad d_2 = 300$

**Figure 1** Optimal clairvoyant vs. non-clairvoyant EDF (left) and clairvoyant vs. CM (right) schedules for the job set of Example 1. EDF incurs WTF of 250, causing  $J_1$  to miss its deadline at 450. CM does not allocate the Lo-criticality  $J_2$  enough execution time earlier in the schedule so as to guarantee its feasibility if the realized scenario is LO, which is the case in this example. This causes  $J_2$  to miss its deadline at time 300.

the feasibility of  $J_1$  (which is the only job whose feasibility matters given that the scenario is of HI criticality). We call this processor time waste—caused by lack of knowledge of the scenario—Work **Threatening Feasibility (WTF)**. In the example, EDF incurred WTF of 250 for the given scenario, caused by scheduling  $J_2$ . The speed-up factor of a given scheduling policy measures its worst case (maximum) incurred WTF across all MC instances that are MC-feasible (on a unit-speed processor). We note that WTF is only incurred for scenarios that have HI criticality behaviors. The problem with CM, on the other hand, is that it does not care about the feasibility of Lo-criticality jobs in light of a Lo behavior, although it causes the system criticality level to be realized the soonest possible.

Our example suggests that to both minimize the WTF and guarantee feasibility, the scheduling policy must strive to achieve a balance between the following conflicting objectives:

- **O1.** It should allocate Lo-criticality jobs sufficiently enough execution times early on; in particular, prior to the  $T_{\text{CI}}$ , so as to guarantee their schedulability in the case where the realized behavior is of Lo criticality, and

- **O2.** It should minimize any WTF, by

- a. driving the revelation of the system criticality level sufficiently quickly by scheduling HI-criticality jobs, so as to decide whether to drop LO-criticality jobs as soon as possible, and

- **b.** minimizing the allocation in O1 if the scenario is HI-criticality (it is here where the objectives are conflicting).

## Probabilistic MC-Model: Justification

The MC model we consider in this article is a probabilistic variant of the MC model thus described. But *why use a probabilistic MC model?* First, the current MC standards and accreditations express the required performance guarantees of MC software components as failure probabilities. For

## 01:6 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

| Level        | Failure Condition | Failure Rate Limit (failures/hour) | Example                 |

|--------------|-------------------|------------------------------------|-------------------------|

| А            | Catastrophic      | $10^{-9}$                          | Fly-by-wire             |

| В            | Hazardous         | $10^{-7}$                          | Fuel management         |

| $\mathbf{C}$ | Major             | $10^{-5}$                          | Pilot/ATC communication |

| D            | Minor             | $10^{-3}$                          | Flight data recorder    |

| Е            | No effect         | n/a                                | Entertainment system    |

**Table 1** DO-178B Criticality Specifications (AdaCore [1]).

instance, the DO-178B avionics standard<sup>1</sup> lists 5 levels of criticality, and specifies for each criticality level an upper bound on the *failure rate* of software components having that criticality (Table 1). From the scheduling perspective, job failures are deadline misses. Then given how MC systems are specified in practice, we believe that a probabilistic framework is the natural setting in which MC systems ought to be framed and reasoned about.

**Note.** Failure rate estimation is a research problem in its own right, but is outside the scope of this article. We refer the reader to Shooman [36] for an in-depth account of failure rate estimation in avionics software systems, along with feasibility studies and the associated analysis.

Second, without any additional information about job demands other than WCET estimates, the scheduler is oblivious to job demand realizations prior to job completion, until the realizations present themselves online at one of the system operational criticality level jump instants. As a consequence, working with WCET estimates solely will lead to underutilization of the processor when the WCETs are not realized.

## Contribution

Whereas the contribution in this specific article relates to a specific restriction of the MC job model, the overall thrust of our work is to develop a framework for reasoning about workload of different criticality levels and providing probabilistic guarantees about the successful execution of jobs. The one-shot *job* model that we consider—as opposed to the more complex *recurrent task model*—was, as we shall see below, studied extensively in the context of MC scheduling, and it remains highly relevant due to the complexity of MC scheduling problems. We have chosen this particular model as a first step towards reasoning about recurring tasks. One can interpret our work as providing the boundaries for synthesizing feasible policies.

This article is an attempt to reconcile the widely used job-dropping model and the mixedcriticality specifications as institued by the current standards and the industry requirements. Baruah's work and ours have following in common: We both regard allocating execution times to Lo-criticality jobs in cases of HI-criticality execution scenarios as undesirable behavior that the scheduling algorithm should avoid. In our model, however, feasibility is defined more generally, and our definition includes Baruah's definition as a special case: We are given upper bounds on the probabilities that jobs at each criticality level miss their deadlines, and one of our goals is to determine a policy under which the probabilities of deadline misses respect the user-supplied failure tolerance parameters. Toward this goal, we introduce the notion of **probably feasible** MC instances in the job dropping model (for the precise definitions, see Definition 4).

<sup>&</sup>lt;sup>1</sup> Titled Software Considerations in Airborne Systems and Equipment Certification, and developed jointly by RTCA SC-167 and EUROCAE WG-12.

We propose an approach for Dual-Criticality job systems that is not deterministic, and uses the probability distribution of job execution times. Our contribution is a model of MC job systems as a **chance-Constrained Markov Decision Process (CMDP)** that then allows us to provide guarantees around jobs meeting their timing constraints with high probability. The chance constraints are sample path constraints on the trajectories of the MDP induced by executing a policy, and they represent the *risk* of missing deadlines at the various criticality levels. We show how to derive a randomized non-stationary Markov scheduling policy that is expected WTF-optimal, by solving a linear program.

This approach can be computationally expensive, but we envisage this as a first step in enabling such probabilistic analysis. Nevertheless, the problem is amenable to approximation, and we briefly outline one method that can be used to obtain approximately optimal and approximately feasible scheduling policies.

## More Literature

Before concluding this section, we mention some prior work related to MC-scheduling and to probabilistic analysis of real-time systems.

Baruah and Vestal [11] showed that for recurrent MC task systems, Earliest Deadline First (EDF) does not dominate Rate-Monotonic (RM), and neither are optimal for scheduling MC tasks in the job dropping model. The Own Criticality-Based Priority (OCBP) algorithm was among the first algorithms designed specifically for the scheduling of (deterministic) MC job systems within the job dropping model [10]. OCBP is a fixed-priority scheduling policy, and it utilizes Audsley's priority assignment scheme [6]. OCBP was shown to be optimal in the class of fixed-priority MC-scheduling algorithms in the speed-up factor, with a speed-up factor of  $(\sqrt{5}+1)/2$  for dual-criticality job system. It was shown that if an instance I is OCBP-schedulable, then it is MC-feasible; thus, correct schedulability by OCBP is sufficient for MC-feasibility, and the correct MC-scheduling policy is given by the OCBP priorities. Conversely, if I is MC-feasible, then OCBP might or might not correctly MC-schedule I; however, if I is MC-feasible, then OCBP can correctly MC-schedule I on a speed  $(\sqrt{5}+1)/2$  processor, or, in other words, OCBP is capable of correctly MC-scheduling the (smaller) instance where every given WCET is divided by the speed-up factor  $(\sqrt{5}+1)/2$ . This quantifies how inexact OCBP is.

The MC-EDF algorithm [37] was shown to dominate OCBP, in the sense that there are (deterministic) MC-feasible instances that are deemed MC-schedulable by MC-EDF but not by OCBP.

Guo and Baruah [22] studied the scheduling of MC jobs (with job dropping) on a single processor with varying speeds. The authors of the latter extended their work to the sporadic task model with implicit deadlines [9]. Chen et al. [15] devised a deadline-tightening technique for scheduling MC sporadic task systems on a unit-speed single processor, wherein virtual deadlines that are shorter than the actual deadlines are assigned to the higher criticality jobs. Again, low(er) criticality tasks may be rejected in order to satisfy the demands of high(er) criticality tasks. We refer the reader to the manuscript by Burns and Davis [14] for the most current and comprehensive overview of MC systems and related problems.

The probabilistic analysis of (non-MC) real-time systems is not new. Díaz et al. [16] analyzed the behavior of fixed-priority (e.g., RM) and dynamic-priority (e.g., EDF) scheduling algorithms for recurrent, stochastically independent tasks when execution times are random variables. The goal of their work is to compute the probability of deadline miss as well as the (random) response-time of every task. See also [17, 18, 19, 31]. Maxim and Cucu-Grosjean [33] extended the probabilistic analysis framework of Díaz et al. [16] for fixed-priority scheduling schemes to task systems where also the minimum inter-arrival times between job invocations as well as task deadlines may be

## 01:8 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

random variables. Their focus was to efficiently compute the response time of each task under the assumption that tasks are stochastically independent. They do so by using convolution of probability distributions as the key underlying mathematical operation.

To the best of our knowledge, there is no work that aims at identifying feasible scheduling policies for MC job systems where job execution times are random. Alahmad et al. [2] were the first to propose the consideration of probabilistic execution times for MC systems. Guo et al. [23] carried out schedulability analysis of EDF applied to recurrent MC task systems, wherein lower priority tasks are given guarantees against failure. The latter is the closest work we are aware of to our efforts in this article. However, our problem is substantially harder, because it is concerned with *synthesizing* MC scheduling policies, as opposed to *analyzing* existing (fixed) scheduling policies.

## 2 System Model

We will adopt Vestal's model described above, but we will frame it in a probabilistic setting. The system we consider is that of n jobs executing upon a single processor, and all jobs are ready to execute at time 0. We will make use of the sets  $\mathbb{N} = \{1, 2, ...\} \subset \{0, 1, 2, ...\} = \mathbb{Z}_+$ . For ease of reference, we give in Table 2 a listing of most of the notation used in this article.

**Note:** The purpose of this section is to present as general a probabilistic framework for MC systems. As such, the exposition to follow will be in terms of general probability spaces, arbitrary number of criticality levels, with no assumptions about the random demands except boundedness. *This setting is, however, much more general than the actual problem that we consider, which is a specialization of the framework to be presented to two criticality levels and discrete demands.*

In addition to the parameters  $(\chi_i, c_i, d_i)$  described earlier, the execution **demand** of job  $J_i$  is described by a random variable

$$\zeta_i : \Omega_i \to (0, c_i(1)] \cup \dots \cup (c_i(\chi_i - 1), c_i(\chi_i)] = (0, c_i(\chi_i)]$$

on a probability space  $(\Omega_i, \mathcal{M}_i, \mathbb{P}_i)$ , where  $\Omega_i$  is the scenario space associated with job  $J_i$  consisting of all possible execution scenarios,  $\mathcal{M}_i$  is the set of possible (observable, measurable) events, and  $\mathbb{P}_i$  is a probability measure on  $\Omega_i$ .

We will assume that the jobs are *independent*; that is, the demand random variables  $\zeta_1, \ldots, \zeta_n$  are independent. The distribution of  $\zeta_i$  is the probability measure  $\mathbb{P}_{\zeta_i} \equiv \mathbb{P}_i \circ \zeta_i^{-1}$  on  $(0, c_i(\chi_i)]$ , and  $\mathbb{P}_{\zeta_i}$  is known. Accordingly, job  $J_i$  is characterized by the tuple  $((\Omega_i, \mathcal{M}_i, \mathbb{P}_i), \zeta_i, \chi_i, c_i, d_i), i \in [n]$ . The actual execution time that a job consumes at run-time (upon completion) is a **job demand realization**. The demand realization of a job is not known prior to its completion. A job **completes** execution when it announces, or signals, that it has finished execution; i.e., when the demand realization has presented itself. The latter happens when the job has been allocated enough execution time to produce its output entirely.

To this end, let

$$\Omega = \prod_{i=1}^{n} \Omega_i, \quad \mathcal{M} = \bigotimes_{i=1}^{n} \mathcal{M}_i,$$

where  $\bigotimes_{i=1}^{n} \mathcal{M}_i$  is the product  $\sigma$ -algebra; that is, the  $\sigma$ -algebra with respect to which all the projection (coordinate) maps  $\operatorname{proj}_i : \Omega \to \Omega_i$  are measurable. Let  $\mathbb{P}$  be the product measure on  $(\Omega, \mathcal{M})$ ; i.e.,  $\mathbb{P}$  is such that for every rectangle  $A \in \mathcal{M}$ , where  $A = A_1 \times \cdots \times A_n$  and  $A_i \in \mathcal{M}_i$ ,

$$\mathbb{P}(A) = \mathbb{P}(A_1 \times \dots \times A_n) = \prod_{i=1}^n \mathbb{P}_i(A_i).$$

(1)

## **Table 2** Notation

| Notation                                                                   | Meaning                                                                                                            |

|----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|

| $\mathbb{Z}_+$                                                             | $: \{0, 1, 2, \dots\}$                                                                                             |

| N                                                                          | $: \{1, 2, \dots\}$                                                                                                |

| $[m]$ , where $m \in \mathbb{N}$                                           | : $\{1,, m\}$                                                                                                      |

| R                                                                          | : The real numbers                                                                                                 |

| $n \in \mathbb{N}$                                                         | : Number of input jobs                                                                                             |

| $c_i(\ell) > 0$                                                            | : WCET estimate of job $J_i$ at criticality level $\ell$                                                           |

| $\chi_i$                                                                   | : Criticality level of job $J_i$                                                                                   |

| $d_i > 0$                                                                  | : Deadline of job $J_i$                                                                                            |

| $\Omega_i$                                                                 | : Scenario space of job $J_i$                                                                                      |

| $\mathcal{M}_i$                                                            | : Set of events; subsets of $\Omega_i$ ( $\sigma$ -algebra)                                                        |

| $\mathbb{P}_i$                                                             | : Probability measure on the scenario space $\Omega_i$ of job $J_i$                                                |

| $\bigotimes_{i=1}^n \mathfrak{M}_i$                                        | : <i>n</i> -fold product $\sigma$ -algebra                                                                         |

| $\mathbb{P}$                                                               | : Probability measure on the product scenario space                                                                |

| $\zeta_i, Z_i$                                                             | : Demand random variables                                                                                          |

| $G_{Z_i}$                                                                  | : Distribution function of random variable $Z_i$                                                                   |

| $\mathbb{E}$                                                               | : Expectation operator with respect to product scenario space                                                      |

| $\mathbb{1}_E(x)$                                                          | : Indicator function of a set <i>E</i>                                                                             |

| $\delta_x(E), E \text{ is a set, } x \text{ a point}$                      | : Dirac measure                                                                                                    |

| · · ·                                                                      |                                                                                                                    |

| proj <sub>i</sub>                                                          | : Projection (coordinate) map, returns <i>i</i> th component of a given vector<br>: All zeros and all ones vectors |

| 0, 1                                                                       |                                                                                                                    |

|                                                                            | : Unit vector whose <i>i</i> th coordinate is 1                                                                    |

| A<br>~                                                                     | : $\{e_1, \ldots, e_n\} \cup 0$ , Action space of the MDP                                                          |

| 5                                                                          | : State space of the MDP                                                                                           |

| $a_t$                                                                      | : $n$ -component vector, action taken at time $t$                                                                  |

| $y_t$                                                                      | : $n$ -component binary vector of job finish signals at time $t$                                                   |

| $x_t$                                                                      | : <i>n</i> -component vector, cumulative execution time allocations up to time                                     |

| $r_t$                                                                      | : scalar error flag                                                                                                |

| $s_t = (t, y_t, x_t, r_t)$                                                 | : State of the MDP at time $t$                                                                                     |

| $A(s_t)$                                                                   | : Admissible actions in state $s_t$                                                                                |

| $\pi(ds_t \mid s_{t-1}, a_{t-1})$                                          | : Markov policy                                                                                                    |

| $Q(ds_t \mid s_{t-1}, a_{t-1})$                                            | : State transition kernel of MDP                                                                                   |

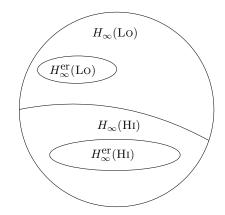

| $H_{\infty}$                                                               | : Canonical trajectory space of the MDP induced by executing policy $\pi$                                          |

| $\{A_t\}, \{S_t\}, \{Y_t\}, \{R_t\}, t \in \mathbb{Z}_+$                   | : Action, state, finish signal, and error stochastic processes on $H_\infty$                                       |

| crit : $\Omega = \prod_{i=1}^n \Omega_i 	o \mathbb{N}$                     | : Scenario criticality level                                                                                       |

| critDemand : $B \equiv \prod_{i=1}^{n} (0, c_i] \to \mathbb{N}$            | : Demand realization criticality level                                                                             |

| $critPath: H_\infty 	o \mathbb{N}$                                         | : System criticality level of trajectory (path)                                                                    |

| $critState:S\to\{\mathrm{Lo},\mathrm{Hi},\mathrm{Unknown}\}$               | : Operational system criticality level given a state                                                               |

| $\mathbb{P}^{\pi}$                                                         | : The (unique) probability measure on $H_{\infty}$                                                                 |

| E <sup>π</sup>                                                             | : Expectation with respect to $H_{\infty}$                                                                         |

| $F_i \equiv F_i^{\pi} : H_{\infty} \to \mathbb{N}$                         | : (Random) Finish time of job $J_i$ with respect to policy $\pi$                                                   |

| $T_{\rm Lo} \equiv T_{\rm Lo}^{\pi} : H_{\infty} \to \mathbb{N}$           | : Earliest time at which Lo system criticality level is inferred by policy                                         |

| $T_{\mathrm{HI}} \equiv T_{\mathrm{HI}}^{\pi} : H_{\infty} \to \mathbb{N}$ | : Earliest time at which HI system criticality level is inferred by policy a                                       |

| $T_{\rm CI} \equiv T_{\rm CI}^{\pi}$                                       | : $\min(T_{\rm Lo}, T_{\rm Hi}), T_{\rm CI}$ of a trajectory in $H_\infty$                                         |

| $w: S \times S \to \mathbb{Z}_+$                                           | : Local (immediate, per stage) objective cost function of MDP                                                      |

| $W \equiv W^{\pi} : H_{\infty} \to \mathbb{Z}_{+}$                         | : WTF random variable on trajectory space                                                                          |

| $\kappa: S \to \{0, 1\}$                                                   | : Immediate constraint cost function of MDP                                                                        |

| $C \equiv C^{\pi} : H_{\infty} \to \mathbb{Z}_{+}$                         |                                                                                                                    |

## 01:10 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

We shall denote vectors  $\omega \in \Omega$  as  $\omega_1, \ldots, \omega_n$ , where  $\omega_i \in \Omega_i$  is the *i*th coordinate of  $\omega$ . We extend every  $\zeta_i$  to be defined on  $\Omega$  as follows. Let  $Z_i = \zeta_i \circ \operatorname{proj}_i$ . Then  $Z_i : \Omega \to (0, c_i(L)]$  depends only on the *i*th coordinate of a given  $\omega \in \Omega$ ; that is,

$$Z_i(\omega) = \zeta_i(\operatorname{proj}_i(\omega)) = \zeta_i(\omega_i) \qquad (\omega \in \Omega).$$

We define the demand vector  $Z = (Z_1, \ldots, Z_n) : \Omega \to \prod_{i=1}^n (0, c_i(L)]$ . Then

$$Z^{-1}(C_1 \times \dots \times C_n) = (Z_1, \dots, Z_n)^{-1}(C_1 \times \dots \times C_n)$$

= { $\omega \in \Omega : Z_i(\omega) \in C_i \quad \forall i \in [n]$ } [=  $\bigcap_{i=1}^n Z_i^{-1}(C_i)$ ]

= { $\omega \in \Omega : \operatorname{proj}_i^{-1}(\omega) \equiv \omega_i \in \zeta_i^{-1}(C_i) \quad \forall i \in [n]$ }

=  $\prod_{i=1}^n \zeta_i^{-1}(C_i).$  (2)

Then the definition of  $\mathbb{P}$  implies that the distribution of Z,  $\mathbb{P}_Z$ , is such that

$$\mathbb{P}_{Z}(C_{1}\cdots C_{n}) = \mathbb{P}\left(Z^{-1}(C_{1}\cdots C_{n})\right) \\ = \mathbb{P}\left(\bigcap_{i=1}^{n} Z_{i}^{-1}(C_{i})\right) = \mathbb{P}\left(\prod_{i=1}^{n} \zeta_{i}^{-1}(C_{i})\right) =_{(*)} \prod_{i=1}^{n} \mathbb{P}_{i}\left(\zeta_{i}^{-1}(C_{i})\right) = \prod_{i=1}^{n} \mathbb{P}_{\zeta_{i}}(C_{i}),$$

where equality (\*) follows by (1).

We will let  $G_{\zeta_i}(t) = \mathbb{P}_{\zeta_i}((-\infty, t])$  denote the **distribution function** of  $\zeta_i$ . In the probabilistic setting, every  $\omega \in \Omega$  is a **scenario** of execution, and  $Z(\omega)$  is the corresponding **system demand realization** (contrast these definitions with their counterparts in the deterministic setting described above). Every execution scenario maps to a unique **system criticality level realization** through the function crit :  $\Omega \to [L]$ , where

$$\operatorname{crit}(\omega) = \min\Big\{\ell \in [L] : Z_i(\omega) \in (0, c_i(\ell)] \text{ for all } i \in [n]\Big\}.$$

(3)

That crit is defined for all scenarios  $\omega \in \Omega$  follows by monotonicity of  $c_i(\ell)$  with respect to  $\ell$ .

Fix  $\ell \in [L]$ . For a scenario  $\omega \in \Omega$ , by (3),  $\operatorname{crit}(\omega) = \ell$  if there is at least one job, say  $J_i$ , such that  $c_i(\ell-1) < Z_i(\omega) \le c_i(\ell)$ , while the remaining jobs are such that  $Z_j(\omega) \le c_j(\ell)$ . For  $\ell \in [L]$ , by independence of job demands,

$$\mathbb{P}(\mathsf{crit} \le \ell) = \mathbb{P}(\bigcap_{i=1}^n \{Z_i \le c_i(\ell)\}) = \prod_{i=1}^n G_{\zeta_i}(c_i(\ell)).$$

Since every scenario has a unique criticality level,

$$\mathbb{P}(\mathsf{crit} \leq \ell) = \sum_{k=1}^{\ell} \mathbb{P}(\mathsf{crit} = k).$$

Therefore,

$$\mathbb{P}(\mathsf{crit} = \ell) = \mathbb{P}(\mathsf{crit} \le \ell) - \mathbb{P}(\mathsf{crit} \le \ell - 1) = \prod_{i=1}^{n} G_{\zeta_i}(c_i(\ell)) - \prod_{i=1}^{n} G_{\zeta_i}(c_i(\ell - 1)),$$

with the convention that  $c_i(0) = 0$ . Specializing to the dual criticality case, where  $\text{Lo} \equiv 1$  and  $\text{HI} \equiv 2$ , we have

$$\mathbb{P}(\mathsf{crit} = \mathrm{Lo}) = \prod_{i=1}^{n} G_{\zeta_i}(c_i(\mathrm{Lo})), \qquad \mathbb{P}(\mathsf{crit} = \mathrm{HI}) = 1 - \prod_{i=1}^{n} G_{\zeta_i}(c_i(\mathrm{Lo})). \tag{4}$$

Now we recast the definitions made earlier in terms of scenarios spaces, random variables, and the functions that we have just defined.

A scheduling policy is a rule that at every time instant decides which job, from the set of available jobs (those that have not finished execution), is assigned the processor. At every time instant, a scheduling policy may use the characterizing parameters of all jobs, as well as its previous decisions, in making its next job allocation decision.

▶ Definition 2 (Correct MC-Schedulability). A policy  $\pi$  is said to correctly MC-schedule an instance  $I = (J_1, \ldots, J_n; L)$  if for every scenario  $\omega \in \Omega$ , every  $J_i$  with  $\chi_i \ge \operatorname{crit}(\omega)$  receives  $Z_i(\omega)$  units of execution during  $[0, d_i]$  under  $\pi$ .

We stress again that this definition does not require that jobs whose criticality is less than that of the realized system criticality level be given any execution; in fact, we will consider doing so as an undesired allocation scheme that is wasting the processor utilization.

▶ **Definition 3** (MC-Feasibility, Classical). An instance  $I = (J_1, \ldots, J_n; L)$  is MC-feasible if there is an online (non-clairvoyant) scheduling policy  $\pi$  under which *I* is correctly MC-schedulable.

Since our setting is probabilistic, we will be concerned with the notions of probabilistic feasibility and *expected* WTF-optimality. We defer the formal definitions of these notions until we have precisely defined the stochastic process induced by a policy, and the underlying probability space over which the expectation is taken (Definitions 4 and 5 in section 3.4).

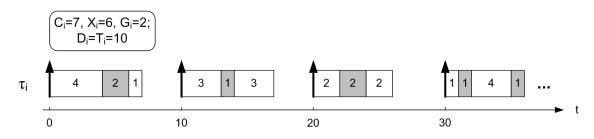

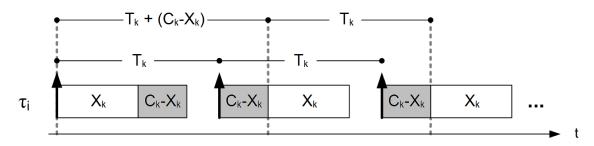

## **3** Problem Definition: Integer Demands and Dual Criticalities

We consider a specialization of the setting discussed in the previous section, in which all demand random variables are integer-valued<sup>2</sup>, and the system is dual-criticality. We are given two error parameters: One is a lower bound on the probability that all n jobs finish at or before their deadlines if the system criticality level is realized as Lo, and the other is a lower bound on the probability that HI-criticality jobs meet their deadlines if the system criticality level is realized as HI. We are required to compute a scheduling policy that minimizes, in expectation, the time wasted scheduling LO-criticality jobs if the system criticality level turns out to be HI, while respecting the deadline miss constraints. That is, we want to compute a policy that minimizes the WTF for the given instance, while respecting the timeliness constraints given by the error parameters. We will make the definition of deadline miss probability precise in sections to follow. Formally, the demand becomes the random variable

$\zeta_i: \Omega_i \to \{1, 2, \dots, c_i(\mathrm{Lo}), c_i(\mathrm{Lo}) + 1, \dots, c_i(\chi_i)\}.$

Accordingly, all demand realizations are integers, and we will therefore consider scheduling at integer boundaries. We shall assume that a job system is MC if not all the input jobs have the same criticality.

## 3.1 MDP Setup

Let  $Y = \{0 : \text{finished}, 1 : \text{not finished}\}^n$ , and let  $y_t \in Y$  be the following variable (*n*-component vector):  $y_t^i = 1$  iff job  $J_i$  still requires execution at time t, and  $y_t^i = 0$  iff  $J_i$  has finished execution. At time 0, all jobs require execution, so we shall assume that  $y_0 = \mathbf{1}$ , the vector of all 1s. The

<sup>&</sup>lt;sup>2</sup> One may equally well work with rational times by regarding time as being divided into integer multiples of some fixed rational quantum q > 0, and using scaling arguments to convert to integers.

## 01:12 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

evolution of the system state depends on the policy, so will specify precisely how the system evolves after formally defining policies.

Let A be the set of control actions (here jobs) available to the scheduler. We will let  $A = \{e_1, \ldots, e_n\} \cup \{\mathbf{0}\}$ , where **0** is the vector of all 0s, and  $\{e_1, \ldots, e_n\}$  is the standard basis for  $\mathbb{R}^n$ ;  $e_i$  is the unit vector that is 1 at the *i*th coordinate and 0 elsewhere. If the action taken at time  $t \in \mathbb{Z}_+$  is  $a_t \in A$ , then  $a_t = e_i$  means that job  $J_i$  occupies the processor during [t, t+1]. If  $a_t = \mathbf{0}$ , then no job is scheduled and the processor is kept idle. Let  $x_t = (x_t^1, \ldots, x_t^n)$  encode the amount of execution time that every job has been allocated up to the beginning of the *t*th epoch (before acting at time *t*); that is,  $x_0 = \mathbf{0}$  and  $x_t = \sum_{m=0}^{t-1} a_m$  for  $t \in \mathbb{N}$ . Then for every  $t \in \mathbb{Z}_+$  and  $i \in [n]$ ,  $x_t^i \in X_i = \{0, 1, \ldots, c_i(\chi_i)\}$ . We will let  $X = \prod_{i=1}^n X_i$ . We will utilize a variable  $r_t$  to "mark" the state as "error". An error flag stamped on a state signifies a deadline miss.  $r_t$  assumes values in

$R = \{$ not error, potential error, error, error' $\}$ .

The state of the scheduling system at time  $t \in \mathbb{Z}_+$  is  $s_t = (t, y_t, x_t, r_t) \in S$ , where  $S \subset \{0, \ldots, N\} \times Y \times X \times R$ . The rationale behind our choice of this particular design of system state will become clear during the derivation of the state process below. For now, we mention how each element comprising our state representation achieves a desirable merit we seek in the system state:

- t: The main reason we include time is that we want to encode job finish times in the state, because we will identify "error" states as those where some job's finish time exceeds its deadline. As a byproduct, augmenting the state with time will result in time-homogeneous (stationary) state transition dynamics (Hernández-Lerma [25], p. 13);

- $y_t$ : Implements the idea that a job *signals* that it has finished execution; this is the only state element that we *observe*, the others we *set* according to  $y_t$ ;

- $x_t$ : Summarizes all we need to know about the decisions we have made (allocations) up to time t, thus eliminating the need to include all actions up to time t. This is the key to ensure that the state process, which we derive below, is a *Markov chain*;

- $r_t$ : One case where a state  $s_t$  becomes error is if some HI-criticality job  $i \in \mathcal{I}_{HI}$  has just missed its deadline, which happens when  $t = d_i$  and  $J_i$  still requires execution  $(y_t^i = 1)$ . In this case, we will set  $r_t = \text{error}$ . When  $r_t = \text{error}$ , we will set  $r_{t'}$  to error' for all t' > t; we do so to avoid charging the trajectory of execution more than once if more then one job miss their deadlines (see (17) and the discussion thereafter). Another possible error scenario is that when some Lo-criticality job  $i \in \mathcal{I}_{Lo}$  has just missed its deadline  $(t = d_i)$  and still demands execution  $(y_t^i = 1)$ , and the system criticality level realization is inferred as Lo at or before t; that is, all HI-criticality jobs have already finished execution with Lo demand realizations  $(y_t^j = 0$  and  $x_j^{\ell} \leq c_j(\text{LO})$  for all  $j \in \mathcal{I}_{\text{HI}}$ . However, those are not the only cases where the state becomes error. Consider the more subtle situation where no job has missed its deadline prior to time t, and  $s_t$  is such that there is  $i \in \mathcal{I}_{Lo}$  that just missed its deadline  $(t = d_i \text{ and } y_t^i = 1)$ , but the scenario's criticality level realization is not yet determinable; in terms of our control variables, there is a non-empty  $F \subset \mathcal{I}_{HI}$ , possibly all of  $\mathcal{I}_{HI}$ , such that every job j in F has executed for at most  $c_j(\text{LO}) - 1$ , and none of the jobs in F have finished execution  $(y_t^j = 1 \text{ and } x_t^j < c_j(\text{LO})$ for all  $j \in F$ ), while the other  $k \in \mathcal{I}_{HI} \setminus F$ , if any, have finished already with LO demand realizations  $(y_t^k = 0 \text{ and } x_t^k \leq c_k(\text{LO}) \text{ for all } k \in \mathcal{I}_{\text{HI}} \setminus F)$ . In this case, the LO-criticality job  $J_i$ that just missed its deadline does not drive the system into an error state at time t since, by our definition of MC feasibility, this cannot be decided until we know the execution scenario's criticality level realization with certainty, which here depends on the (yet unknown) demand realizations of the jobs in F. In such case, we will say that the system is *potentially* in error state at time t, and we set  $r_t = potential error$  to "remember" that a Lo-criticality job has

missed its deadline at t. Doing so gives us the facility to decide later whether or not the system is in error state—as soon as the scenario's criticality level realization is inferred—and, as a consequence, deduct the penalties correctly in the MDP.

For  $t \in \mathbb{N}$ , let  $(S \times A)^t$  be the Cartesian product of  $S \times A$  with itself t times. Define the set of admissible histories up to time t as  $H_0 = S$ , and

$$H_t = (\mathsf{S} \times \mathsf{A})^t \times \mathsf{S} \qquad (t \in \mathbb{N}).$$

Every element of  $H_t$  is called a *t***-history**, and has the form

$h_t = (s_0, a_0, \dots, s_{t-1}, a_{t-1}, s_t).$

t-histories are the information available to the scheduler before making its job selection decision at time t.

Let  $A(s_t) \subset A$  be the set of actions that the scheduler is allowed to apply at time t when the scheduling system is in state  $s_t$ . We shall call  $A(s_t)$  the set of **admissible actions** in state  $s_t$ . A **scheduling policy** is a sequence  $\pi = \{\pi_t : t \in \mathbb{Z}_+\}$ , where  $\pi_t$  is a stochastic kernel on  $A(s_t)$  given  $H_t$ . That is, if we denote the power set of a set X as  $2^X$ , then  $\pi_t \equiv \pi_t(da_t \mid h_t)$ , where  $\pi_t : 2^{A(s_t)} \times H_t \to [0, 1]$  is such that

(i) for every  $B \in 2^{\mathsf{A}(s_t)}$ ,  $\pi_t(B \mid \cdot)$  is a function from  $H_t$  to [0, 1], and

(ii) for every  $h_t \in H_t$ ,  $\pi_t(\cdot \mid h_t) : 2^{\mathsf{A}(s_t)} \to [0,1]$  is a probability measure on  $\mathsf{A}(s_t)$ .

The state  $s_t$  summarizes all allocation decisions and remaining demands up to time t. We will restrict our attention to *Markov* policies, where  $\pi_t(a_t|h_t) = \pi_t(a_t|s_t)$  for every  $h_t$  ([26] Definition 2.3.2 a).

**A Note on Terminology:** Since our state and action spaces are finite, all the stochastic (transition) kernels here can be represented by *transition matrices*. In this article, however, we will not use any of the matrix algebra machinery used to analyze Markov chains, so we will present our framework in the language of stochastic kernels.

A work-conserving scheduling policy always schedules a job that still demands execution; i.e., it never keeps the processor idle whenever there is a job that has not finished execution. Thus a policy is non-work-conserving iff there is  $t \in \mathbb{Z}_+$  such that  $a_t = \mathbf{0}$  (no job is selected) and there is  $i \in [n]$  such that  $J_i$  has not finished execution; i.e.,  $y_t^i = 1$ . The epoch  $N = \sum_{i=1}^n c_i(\chi_i)$  is an upper bound on our planning horizon. With N fixed, any trajectory induced by executing a work conserving policy satisfies 1)  $\sum_{i=1}^n x_t^i = t$  for every  $t \in \{0, \ldots, N\}$  for which  $y_t^i = 1$  for some  $i \in [n]$ , and 2)  $x_t = x_T$  for all  $t \in \{T, \ldots, N\}$ , where T is the first time instant at which all jobs finish execution. A non-work-conserving schedule will only delay job completions and the time at which the criticality level realization can be inferred, so we restrict ourselves to work-conserving policies.

We implement the requirement that the scheduling policy be work-conserving by specifying that  $A(s_t)$  includes only vectors  $e_i$  for which  $y_t^i = 1$ , if any. We will *drop* Lo-criticality jobs (temporarily) as soon as the state  $s_t$  indicates that the operational system criticality level is HI, and we will enforce this by placing further restrictions on  $A(s_t)$ . Namely, given state  $s_t$ , if there is  $i \in \mathcal{I}_{\text{HI}}$  such that both  $x_t^i \ge c_i(\text{LO})$  and  $y_t^i = 1$ , then the operational system criticality level at time t is HI and there are HI-criticality jobs still requiring execution, so we exclude from  $A(s_t)$  all Lo-criticality jobs. Otherwise, we include all Lo-criticality jobs that have not finished yet. If  $s_t$ does not satisfy the latter condition, then either the system criticality level realization cannot be inferred at t, or all HI-criticality jobs finished with LO demand realizations before or at t, or the

#### 01:14 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

system criticality level was known before or at t as HI, but all HI-criticality jobs have finished execution at t. In the last case, we might have dropped LO-criticality jobs earlier, and, since scheduling LO-criticality jobs at time t in this case is not considered WTF (and does not affect feasibility), we may bring back any LO-criticality jobs that still need to execute. In summary,

$$\mathsf{A}(s_t) = \begin{cases} \{e_i : y_t^i = 1, \chi_i = \mathrm{HI}\} & (*) \text{ if there is } i \in \mathcal{I}_{\mathrm{HI}} \text{ such that } x_t^i \ge c_i(\mathrm{LO}) \text{ and } y_t^i = 1 \\ \{e_i : y_t^i = 1\} & \text{ if } (*) \text{ not satisfied and there is } i \in [n] \text{ such that } y_t^i = 1 \\ \{\mathbf{0}\} & \text{ otherwise (all jobs finished execution).} \end{cases}$$

## **Control Model**

Scheduling decisions are made at every  $t \in \{0, ..., N-1\}$  exclusively. If a certain job is chosen to execute at some t, then this job occupies the processor for the duration [t, t+1], without interruption, until the scheduler is invoked again at t+1. We call [t, t+1] the tth **control interval**. At any t > 0, if job  $J_i$  was chosen to occup the processor during [t-1, t] (i.e.,  $a_{t-1} = e_i$ ), then the scheduler knows at time t whether or not job  $J_i$  requires more execution by observing the value of  $y_t^i$ , which will be set to finished if job  $J_i$  signals that it has finished execution at time t. The other jobs' demands are not affected by scheduling job  $J_i$ , and whether or not the other jobs require more execution does not change in [t-1, t]. The information available to the scheduler at the beginning of the tth control interval is  $a_{t-1}, y_t, x_t$ , and  $r_t$ .

Let s = (t, y, x, r) and  $\hat{s} = (\hat{t}, \hat{y}, \hat{x}, \hat{r})$ . It is necessary for transition  $(s, a, \hat{s})$  to be valid that all the following be satisfied:

$$\begin{split} \mathbf{NC}: \quad & \hat{t} = t + 1, \\ & \sum_{i=1}^{n} x^{i} = t, \\ & a = \hat{x} - x = e_{i} \text{ for some } i \in [n], \text{ or } a = \hat{x} - x = \mathbf{0} \\ & y - \hat{y} \in \{\mathbf{0}, e_{i}\} \text{ for the same } i, \text{ and} \\ & (r, \hat{r}) \notin \{(\text{error, not error}), (\text{error, potential error}), (\text{not error, error'}), \\ & (\text{potential error, error'}), (\text{error', r}) \forall r \in \mathbb{R} \setminus \{\text{error'}\} \}. \end{split}$$

However, not all state transitions satisfying **NC** are valid, as we will describe below. All invalid state transitions have  $Q(\{\hat{s}\} \mid s, a) = 0$ , however. To this end, we note that the state includes all the information necessary to determine whether or not the system criticality level is inferred, and if so, determine its value. To simplify the exposition, we define a function critState :  $S \rightarrow \{LO, HI, UNKNOWN\}$ , where critState(s) is the system criticality level realization, and is defined as follows: For s = (t, x, y, r),

- (1) critState(s) = Lo if all HI-criticality jobs finished execution with Lo demand realizations; that is, if  $y^i = 0$  and  $x^i \le c_i(\text{Lo})$  for all  $i \in \mathcal{I}_{\text{HI}}$ ;

- (2)  $\operatorname{critState}(s) = \operatorname{HI}$  if either

- (i) there is  $i \in \mathcal{I}_{HI}$  such that  $x^i(LO) = c_i(LO)$  and  $y^i = 1$ , or

- (ii) there is  $i \in \mathcal{I}_{HI}$  such that  $x^i(LO) > c_i(LO)$ ;

- (3) If neither of the above holds, then critState(s) = UNKNOWN.

Now assuming transition  $(s, a, \hat{s})$  satisfies **NC**, we will use monotonicity of  $t \mapsto x_t$  and  $t \mapsto y_t$ , and that  $s_0$  is fixed, to list additional conditions regarding the error flags under which  $(s, a, \hat{s})$  is a valid transition in an exact sense. In what follows, for a state s = (t, x, y, r) and  $\ell \in \{\text{LO}, \text{HI}\}$ , the statement "an  $\ell$ -criticality job misses its deadline at time t" is to be understood formally as "there is  $i \in \mathcal{I}_{\ell}$  such that  $d_i = t$  and  $y^i = 1$  (not finished)."

- **E1.**  $(r = \text{not error}, \hat{r} = \text{potential error})$ : If all of the following conditions hold:

- (i) no HI-criticality job misses its deadline at time  $\hat{t} = t + 1$ ,

- (ii) a LO-criticality job misses its deadline at time  $\hat{t}$ , and

- (iii) the system criticality level is not yet determinable at  $\hat{t}$ ; that is, critState( $\hat{s}$ ) = UNKNOWN ( $r = no \text{ error says that no HI-criticality jobs missed their deadlines up to time <math>t$ );

- **E2.**  $(r = \text{not error}, \hat{r} = \text{error})$ : Either

- (i) a HI-criticality job misses its deadline at time  $\hat{t}$ , or

- (ii) a Lo-criticality job misses its deadline at time  $\hat{t}$  and critState( $\hat{s}$ ) = Lo;

- **E3.**  $(r = \text{potential error}, \hat{r} = \text{error})$ : Same as 2, except that we dispense with the condition in 22ii that a Lo-criticality job misses its deadline at time  $\hat{t}$ . r = potential error is saying that no HI-criticality job missed its deadline till t, and the criticality level could not be inferred till t, but a Lo-criticality job has missed its deadline already;

- **E4.**  $(r = \text{potential error}, \hat{r} = \text{potential error})$ : Same as conditions (i) + (iii) of E1;

- **E5.**  $(r = \text{potential error}, \hat{r} = \text{not error})$ : If  $\text{critState}(\hat{s}) = \text{HI}$  and no HI-criticality job misses its deadlines at time  $\hat{t} = t + 1$ ;

- **E6.**  $(r = \text{not error}, \hat{r} = \text{not error})$ : The combined conditions of  $(r = \text{not error}, \hat{r} \neq \text{potential error})$ and  $(r = \text{not error}, \hat{r} \neq \text{error})$ ;

- **E7.**  $(r = \text{error}, \hat{r} = \text{error'})$ : always;

- **E8.**  $(r = \text{error}', \hat{r} = \text{error}')$ : always.

The following summarizes the control model:

- 1. At t = 0, all jobs are ready to execute and they all demand execution, and the scheduler needs to pick a job to schedule for exactly one time unit before it is invoked again at t = 1 (i.e.,  $a_0$  needs to be set). Then  $y_0 = 1$ ,  $x_0 = 0$ , and  $r_0 = no$  error;

- **2.** At the beginning of the *t*th control interval:

- **2.1 Update** the cumulative system allocation by setting  $x_t \leftarrow x_{t-1} + a_{t-1}$ ;

- **2.2 Observe** (acquire)  $y_t$ ;

- **2.3 Set Error:** Set  $r_t$  given  $r_{t-1}$  according to one of E1–E8;

- **2.4 Act**: Set  $a_t$  to one of the vectors in  $A(s_t)$ .

We will say that a state is **valid** if it can be generated by the control model above. The state space S contains only the valid states; i.e., S is the subset of  $\{0, \ldots, N\} \times X \times Y \times R$  that can be generated by the control model. For instance, if s = (t, x, y, r) is such that  $t = d_i + 1$  and  $y^i = 1$  (not finished) for some  $i \in [n]$ , and r =not error, then for no x is s is valid, even if x is such that  $\sum_{j=1}^{n} x^j = t$  (necessary for a state to be valid) and  $x^j < c_j(\chi_j)$  for all j.

We point out that the state transition diagram has the simple structure of a directed tree of depth at most N (the maximum horizon length), with fixed root  $s_0$ , and each node in level t,  $t \in \{0, \ldots, N\}$ , corresponds to a possible state at time t (i.e.,  $s_t$ .) Each intermediate node (state) has at most  $|\mathbf{A}||\mathbf{Y}| = 2n$  children, each corresponding to a unique current action and next finish signal pair  $(a_t, y_{t+1})$ . Note that the next cumulative allocation vector,  $x_{t+1}$ , and the next error flag,  $r_{t+1}$ , are deterministic once we know  $a_t$  and  $y_{t+1}$ , so there is only one choice for each given  $s_t$  and  $a_t$ .

## 3.2 The Transition Probabilities

We describe the evolution of the system state by a transition kernel (transition matrix)  $Q(d\hat{s}|s, a)$ :  $2^{\mathsf{S}} \times (\mathsf{S} \times \mathsf{A}) \rightarrow [0, 1]$ . Since our state space  $\mathsf{S}$  is finite, transition kernel Q should satisfy the following for *fixed* action a and previous state s,

**Q1.**  $Q(\emptyset|s, a) = 0;$ **Q2.**  $Q(\mathsf{S}|s, a) = 1;$

## 01:16 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

**Q3.**  $Q(U|s, a) = \sum_{\hat{s} \in U} Q(\{\hat{s}\}|s, a)$  for every  $U \subset \mathsf{S}$ ; **Q4.**  $0 \leq Q(U|s, a) \leq Q(V|s, a) \leq 1$  for every  $U \subset V \subset \mathsf{S}$ . We shall abuse notation and write  $Q(\hat{s}|s, a)$  for  $Q(\{\hat{s}\}|s, a)$ . Let  $(s, a, \hat{s})$  be a valid transition. If s = (t, y, x, r), then  $\hat{t} = t + 1$ , and we shall use the more time-suggestive notation  $\hat{s} \equiv s_{t+1}$ , where  $\hat{y} \equiv y_{t+1}, \hat{x} \equiv x_{t+1}$  and  $\hat{r} \equiv r_{t+1}$ , and we similarly denote s as  $s_t$ . If  $(s, a, \hat{s})$  is not valid, then  $Q(\hat{s}|s, a) = 0$ . Fix an action  $a_t = e_i$ . Then for transition  $(s_t, e_i, s_{t+1})$  to be valid, we must have  $y_t^i = 1$  and  $x_{t+1}^i = x_t^i + 1$ . Also, scheduling  $J_i$  does not affect the execution time demands of the other jobs, so  $s_{t+1}$  must satisfy  $y_t^j = y_{t+1}^j$  for every  $j \neq i$ . For our fixed state-action pair  $(s_t, e_i)$ , we know at time t that  $Z_i > x_t^i$ , and for  $j \neq i$ ,  $Z_j \in C_j$  for some  $C_j \subset [c_j(\chi_j)]$ . The following is a complete list of all the possible next states  $s_{t+1}$  and the corresponding transition probabilities for the fixed action-state pair  $(s_t, a_t = e_i)$  (it is here where we fully utilize the assumption of independent job demands):

■  $y_{t+1}^i = 1$  (not finished): This says that the scenario  $\omega$  is such that  $Z_i(\omega) > x_{t+1}^i = x_t^i + 1$ , and since  $Z_j(\omega)$  remains in  $C_j$  for every  $j \neq i$  at time t+1, we have

$$Q(s_{t+1}|s_t, e_i) = \mathbb{P}(Z_i > x_t^i + 1, Z_j \in C_j \ \forall j \neq i \mid Z_i > x_t^i, Z_j \in C_j \ \forall j \neq i)$$

$$= \frac{\mathbb{P}(Z_i > x_t^i + 1, Z_j \in C_j \ \forall j \neq i)}{\mathbb{P}(Z_i > x_t^i, Z_j \in C_j \ \forall j \neq i)}$$

$$= \frac{\mathbb{P}(Z_i > x_t^i + 1)\mathbb{P}(Z_j \in C_j \ \forall j \neq i)}{\mathbb{P}(Z_i > x_t^i)\mathbb{P}(Z_j \in C_j \ \forall j \neq i)}$$

$$= \frac{\mathbb{P}(Z_i > x_t^i + 1)}{\mathbb{P}(Z_i \geq x_t^i + 1)}$$

(5)

if  $x_t^i < c_i(\chi_i) - 1$ , and  $Q(s_{t+1}|s_t, e_i) = 0$  otherwise. The second to last equality follows by independence of job demands.

$y_{t+1}^i = 0$  (finished): Here the demand of job  $J_i$  is realized at time t + 1; that is, we know that the scenario  $\omega$  is such that  $Z_i(\omega) = x_{t+1}^i = x_t^i + 1$ . Using the same reasoning as in the previous case,

$$Q(s_{t+1}|s_t, e_i) = \begin{cases} \frac{\mathbb{P}(Z_i = x_t^i + 1)}{\mathbb{P}(Z_i \ge x_t^i + 1)} & \text{if } x_t^i < c_i(\chi_i) - 1, \\ 1 & \text{if } x_t^i = c_i(\chi_i) - 1 \\ 0 & \text{otherwise.} \end{cases}$$

(6)

Then for fixed  $(s_t, a_t = e_i)$ , summing over all possible next states; i.e., adding (5) and (6), we have

$$\frac{\mathbb{P}(Z_i > x_t^i + 1) + \mathbb{P}(Z_i = x_t^i + 1)}{\mathbb{P}(Z_i \ge x_t^i + 1)} = \frac{\mathbb{P}(Z_i \ge x_t^i + 1)}{\mathbb{P}(Z_i \ge x_t^i + 1)} = 1.$$

That is, our prescribed transition kernel Q satisfies property Q2, and indeed all the others.

## 3.3 The Underlying Probability Space

In this section we will outline in detail the construction of the probability space that we will be working with. We will shift our attention from scenario spaces (the  $\Omega_i$ s, section 2) to *trajectory spaces*, which consist of the sample paths induced by executing policies. We will need this construction when stating the formal definition of our problem, and we shall make several references to it. Readers acquainted with the theory of Markov decision processes may only wish to familiarize themselves with our notation.

Consider the product space

$$(\mathsf{S} \times \mathsf{A})^{\infty} = \prod_{t=0}^{\infty} (\mathsf{S}_t \times \mathsf{A}_t),$$

where  $S_0 = \{s_0\}$ ,  $s_0 \equiv (t = 0, x_0 = 0, y_0 = 1, r_0 = \text{not error})$  is our *fixed* initial state (all jobs are allocated 0 execution time and they all require execution,)  $S_t \subset \{t\} \times Y \times X \times R$ , and  $A_t$  is a copy of A. We will consider the subset of  $(S \times A)^{\infty}$  where each sequence of state-action pairs can be generated by our control model, and we will call such sequences the **valid trajectories**. We denote the set of valid trajectories as  $H_{\infty}$ , and we call  $H_{\infty}$  the **trajectory space** induced by all work-conserving scheduling policies. Every  $h \in H_{\infty}$  is a trajectory induced by executing some work-conserving policy, and is of the form

$$h = (s_0, a_0, s_1, a_1, \dots).$$

That is, every h is a realization of a schedule. We endow  $H_{\infty}$  with the product  $\sigma$ -algebra, which we denote as  $\mathcal{H}_{\infty}$ . Let  $S_t : H_{\infty} \to \mathsf{S}$  be the projection (coordinate) map on  $H_{\infty}$  such that  $S_t(h) = s_t$ ,  $h \in H_{\infty}$ . Define  $A_t : H_{\infty} \to \mathsf{A}(s_t)$  similarly. Given policy  $\pi = \{\pi_t : t \in \mathbb{Z}_+\}$ , transition kernel Q, and initial distribution  $\nu$  on  $\mathsf{S}$ , the Ionescu-Tulcea extension theorem ([32], Theorem 14.32; [5], Theorem 2.7.2) asserts that there exists a *unique* probability measure  $\mathbb{P}^{\mu}_{\nu}$  on  $H_{\infty}$  such that

$$\mathbb{P}_{\nu}^{\pi}(S_t \in U \mid h_{t-1}, a_{t-1}) = Q(U|s_{t-1}, a_{t-1}) \qquad (U \subset \mathsf{S}).$$

We have  $\nu = \delta_{s_0}$  for  $s_0 = (0, 0, 1, \text{not error})$ , where  $\delta_{s_0}$  is Dirac measure on  $H_{\infty}$ , so for brevity we write  $\mathbb{P}^{\pi} \equiv \mathbb{P}^{\pi}_{\delta_{s_0}}$ . We denote expectation with respect to  $\mathbb{P}^{\pi}$  (on  $H_{\infty}$ ) as  $\mathbb{E}^{\pi}$ . Moreover, because every policy is Markov as mentioned above, it follows that the induced state process  $\{S_t : t \in \mathbb{Z}_+\}$  is a Markov chain for every policy  $\pi$ . That is, for every  $U \subset S$  and  $t \in \mathbb{Z}_+$ ,

$$\mathbb{P}^{\pi}(S_{t+1} \in U \mid s_t, \dots, s_0) = \mathbb{P}^{\pi}(S_{t+1} \in U \mid s_t) = Q(U|s_t, \pi_t),$$

where for fixed  $s_t$ ,

$$Q(U|s_t, \pi_t) = \int_{\mathsf{A}} Q(U|s_t, a_t) \, \pi_t(da_t|s_t) = \sum_{i=1}^n Q(U|s_t, e_i) \, \pi_t(e_i|s_t).$$

From now on, all subsequent random variables will be defined on  $H_{\infty}$ .

▶ Remark. For a given  $s_t$ , each action random variable  $A_t$  of the induced action process  $\{A_t : t \in \mathbb{Z}_+\}$  is distributed according to  $\pi_t(\cdot | s_t)$ ; that is,  $\mathbb{P}^{\pi}(A_t \in C | S_t = s_t) = \pi_t(C | s_t)$  for every  $C \subset \mathsf{A}(s_t)$ .

## 3.4 Problem Statement

We start by formally defining the random variables that make up our objective function and constraints, in terms of the induced MDP. First, we note that to every trajectory corresponds at least one scenario in  $\Omega$ , and that all scenarios that correspond to a trajectory have the same criticality level. Consequently, we define the criticality level of a trajectory as the criticality level of any scenario corresponding to it<sup>3</sup>.

<sup>&</sup>lt;sup>3</sup> To ensure that the trajectory criticality level is well-defined, we must assume that every policy assigns every HI-criticality job the processor for at least  $c_i(\text{LO})$  time units. However, this is readily satisfied by every policy since, by the way we specified the set of admissible actions  $A(s_t)$ , HI-criticality jobs are never dropped.

## 01:18 Risk-Aware Scheduling of Dual Criticality Job Systems Using Demand Distributions

To this end, let  $\mathcal{I}_{\ell} = \{i \in [n] : \chi_i \geq \ell\}$ . Let  $h \in H_{\infty}$  be a trajectory of execution. If h's criticality level is HI, then the earliest time at which this can be inferred is the first instant at which some job  $J_i$  with  $\chi_i = \text{HI}$  demands more than  $c_i(\text{LO})$  units of execution. We denote this random time as  $T_{\text{HI}} : H_{\infty} \to \mathbb{N} \cup \{\infty\}$  and, in accordance with our control model, we define it as